# Asynchronous Sigma Delta Modulators for Data Conversion

#### Wei Chen

Imperial College London

Department of Electrical and Electronic Engineering

Submitted in Partial Fulfilment of the Requirements for the Degree of

Doctor of Philosophy in Electrical and Electronic Engineering of Imperial College London

and the Diploma of Imperial College London

## **Declaration of Originality**

I hereby declare that this thesis and the work reported herein was composed by and originated entirely from me. Information derived from the published and unpublished work of others has been acknowledged in the text and references are given in the list of sources.

## **Copyright Declaration**

The copyright of this thesis rests with the author and is made available under a Creative Commons Attribution Non-Commercial No Derivatives licence. Researchers are free to copy, distribute or transmit the thesis on the condition that they attribute it, that they do not use it for commercial purposes and that they do not alter, transform or build upon it. For any reuse or redistribution, researchers must make clear to others the licence terms of this work

### Acknowledgements

I would like to express my gratitude to my supervisor: Dr. Christos Papavassiliou, for his intelligent guidance. His valuable suggestion help me to get out of the depression, and accomplish this work.

I would also like to thank Dr. Liu Yan and Dr. Alex for their suggestion during the period of designing the circuits for the Gm-C filter. In additional, I would like to thank Dr. Liu Yan for sharing the resources of his Lab.

I also wish to thank Xiao and James for their technical support for software issues and servers maintenance.

I would like to thank CSC of China for their financial support during four years life and study.

Finally, I would like to thank my wife Jane, my parents for their love, support and motivation.

### **Abstract**

The research carried out in this thesis focuses on introducing solutions to solve issues existed in asynchronous sigma delta modulators including complex decoding scheme, lacking of noise shaping and effects of limit cycle components. These issues significantly limit the implementation of ASDMs in data conversion.

The first innovation in this work is the introduction of a novel decoding circuit to digitise the output signal of the asynchronous sigma delta modulator. Compared with the conventional decoding schemes, the proposed one does not limit the input dynamic range of ASDMs, and can obtain a high resolution without a fast sample clock. The proposed decoding circuit operates asynchronously and can measure the duty cycle of the modulated square wave without measuring its instantaneous period.

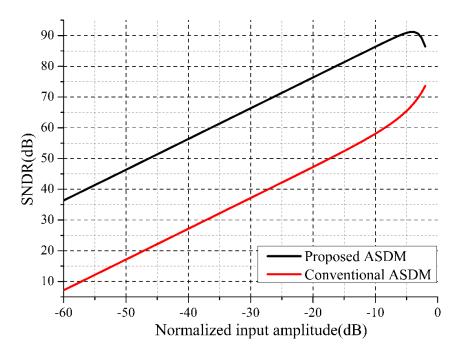

The second innovation of this work is the introduction of a novel architecture of the asynchronous sigma delta modulator with noise shaping without an additional loop filter. Moreover, the proposed modulator requires only a single-bit digital-to-time converter in the feedback loop even for a multi-bit quantiser. The quantiser in the modulator is realized by an eight-phase poly-phase sampler in order to reduce the requirement of the sample clock. Simulation demonstrate that the SNDR of the proposed modulator can be improved by 20dB.

The final innovation of this work is the introduction of frequency compensation to the asynchronous sigma delta modulator. In this proposed modulator, the limit cycle frequency is controlled by the delay time of a novel high linear performance delay line, which is operated in current mode. The compensation is realized by adjusting the equivalent delay time for different input voltage values. The proposed one can double the signal bandwidth with the same limit cycle frequency.

### **Contents**

| Declaration of Originality                                     | 2             |

|----------------------------------------------------------------|---------------|

| Copyright Declaration                                          | 3             |

| Acknowledgements                                               | 4             |

| Abstract                                                       | 5             |

| List of Tables.                                                | 9             |

| List of Figures                                                | 10            |

| List of Symbols                                                | 15            |

| Introduction                                                   | 18            |

| 1.1 Motivation                                                 |               |

| 1.2 Objectives                                                 | 19            |

| 1.3 Outline of this thesis                                     |               |

| Sigma Delta Modulation Fundamentals                            | 22            |

| 1.4 Introduction                                               | 22            |

| 1.5 Synchronous sigma delta modulators                         | 22            |

| 1.5.1 Discrete-time sigma delta modulator                      | 22            |

| 1.5.2 Continuous-time sigma delta modulator                    | 24            |

| 1.6 State of the art for the synchronous sigma delta modulator | 28            |

| 1.7 Asynchronous sigma delta modulators                        | 32            |

| 1.7.1 System analysis                                          | 33            |

| 1.7.2 Noise performance                                        | 38            |

| 1.7.3 Propagation delay                                        | 43            |

| 1.7.4 The state-of-art of asynchronous sigma delta modulators  | 48            |

| 1.8 Summary                                                    | 50            |

| The Asynchronous Sigma Delta Modulator with a Novel Tir        | ne-to-Digital |

| Converter                                                      | 51            |

| 1.9 Introduction                                               |               |

| 1.10 Time signal processing                                    |               |

| 3.2.1 Coarse counting                                          |               |

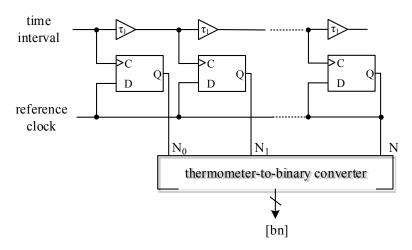

| 3.2.2 Flash time-to-digital converter                                   | 54  |

|-------------------------------------------------------------------------|-----|

| 3.2.3 Coarse-fine time-to-digital converter                             | 55  |

| 3.2.4 Cyclic pulse-shrinking time-to-digital converter                  | 57  |

| 1.11 Time-to-digital converter using vernier delay lines                | 58  |

| 1.11.1 System level design                                              | 59  |

| 1.11.2 Vernier delay lines                                              | 61  |

| 1.11.3 Noise performance                                                | 64  |

| 1.11.4 Demodulation algorithm                                           | 66  |

| 1.11.5 Limitations                                                      | 69  |

| 1.12 Circuit design                                                     | 71  |

| 1.12.1 Asynchronous sigma delta modulator                               | 71  |

| 1.12.2 Time-to-digital converter based on vernier delay lines           | 79  |

| 1.13 Summary                                                            | 86  |

| The Asynchronous Sigma Delta Modulator with Noise Shaping               | 88  |

| 1.14 Introduction                                                       | 88  |

| 1.15 Conventional asynchronous sigma delta modulator with noise shaping | 88  |

| 1.16 A novel asynchronous sigma delta modulator with noise shaping      | 92  |

| 1.16.1 System analysis                                                  | 93  |

| 1.16.2 System level design                                              | 101 |

| 1.16.3 Non-ideal effects in proposed ASDM                               | 104 |

| 4.3.4 Circuit level design                                              | 105 |

| 1.17 Summary                                                            | 112 |

| The Asynchronous Sigma Delta Modulator with Constant Frequency          | 113 |

| 1.18 Introduction                                                       | 113 |

| 1.19 Asynchronous sigma delta modulators with delay cell                | 114 |

| 1.20 The proposed asynchronous sigma delta modulator                    | 117 |

| 1.20.1 Frequency compensation                                           | 117 |

| 1.20.2 Non-ideal effects.                                               | 120 |

| 1.20.3 SNDR comparison                                                  | 128 |

| 1.21 Circuits level design                                              | 130 |

| 1.21.1 Loop filter and comparator                                       | 130 |

|                                                                         |     |

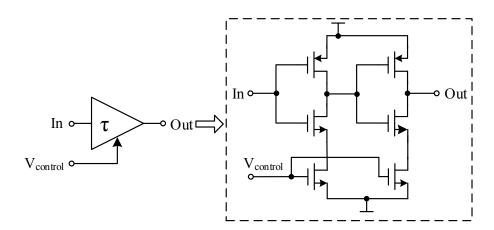

| 1.21.2 The proposed voltage controlled delay line (VCDL) | 132 |

|----------------------------------------------------------|-----|

| 1.21.3 Transistor-level simulation                       | 139 |

| 1.22 Summary                                             | 142 |

| Conclusions                                              | 143 |

| 1.23 Conclusion                                          | 143 |

| 1.24 Future work                                         | 145 |

| Appendix                                                 | 147 |

| Appendix I                                               | 147 |

| 1. DC analysis                                           | 147 |

| 2. Sine wave signal input                                | 147 |

| 3. Distortion                                            | 150 |

| Appendix II                                              | 151 |

| Reference.                                               | 153 |

## **List of Tables**

| Table 2-1: Example of z-domain and s-domain sigma delta modulator transformation | 26   |

|----------------------------------------------------------------------------------|------|

| Table 2-2: Comparison between DT-SDM and CT-SDM                                  | 27   |

| Table 2-3: State of the art of synchronous sigma delta modulators                | 31   |

| Table 2-4: Comparison between ASDM and CT-SDM                                    | 32   |

| Table 3-1: Transistors sizes in the proposed OTA                                 | 75   |

| Table 3-2: Transistors sizes in the proposed comparator with hysteresis          | 77   |

| Table 3-3: Simulation results for the ASDM                                       | 79   |

| Table 4-1: Comparison between ASDM with/without noise shaping and synchronous CT | -SDM |

|                                                                                  | 92   |

| Table 4-2: Main parameters of the integrator and comparator                      | 106  |

| Table 4-3: Sizes of transistors in one delay element                             | 108  |

| Table 4-4: Simulation delay times of the logic gates                             | 110  |

| Table 4-5: Estimation of power consumption of the proposed ASDM                  | 111  |

| Table 5-1: values of parameters in the simulation                                | 129  |

| Table 5-2: Sizes of transistors in the comparator                                | 131  |

| Table 5-3: Main parameters of the comparator                                     | 131  |

| Table 5-4: Sizes of transistors in the voltage-to-current converter              | 134  |

| Table 5-5: Sizes of the transistors in the delay element                         | 136  |

| Table 5-6: Electrical simulation results for VCDL                                | 139  |

# **List of Figures**

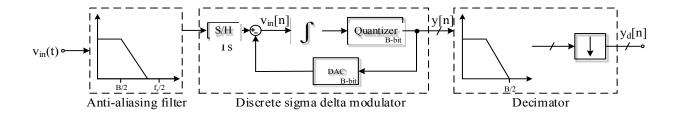

| Figure 2-1: Block diagram of a discrete-time sigma delta analogue-to-digital converter               | . 23 |

|------------------------------------------------------------------------------------------------------|------|

| Figure 2-2: Basic configuration of the continuous-time sigma delta modulator with multi-bit          |      |

| quantiser                                                                                            | . 25 |

| Figure 2-3: Digital-to-analogue converter wave forms for RZ, NRZ, and HZ                             | . 26 |

| Figure 2-4: SNDR and signal bandwidth of recently published synchronous sigma delta                  |      |

| modulators                                                                                           | . 29 |

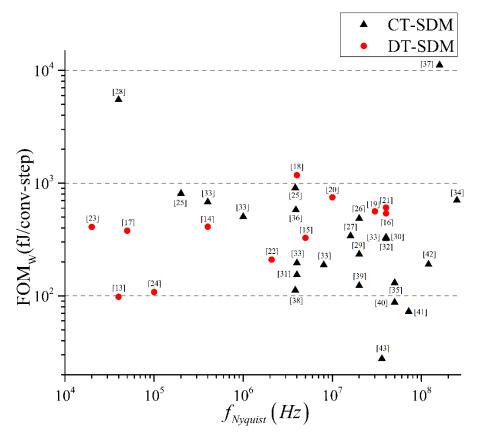

| Figure 2-5: FOMw versus Nyquist output frequency                                                     | . 30 |

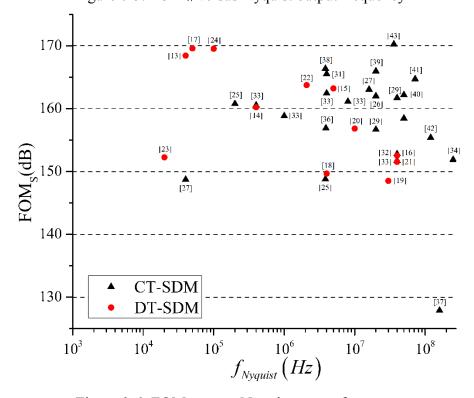

| Figure 2-6: FOMs versus Nyquist output frequency                                                     | . 30 |

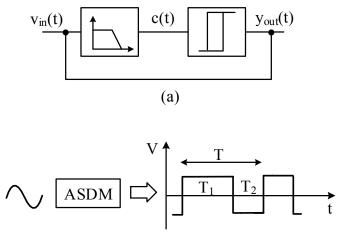

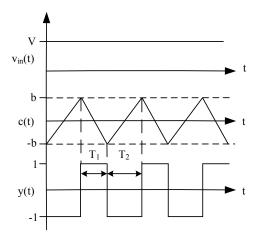

| Figure 2-7: (a) System diagram and (b) Timing diagram of the ASDM                                    | . 33 |

| Figure 2-8: Timing diagram of the asynchronous sigma delta modulator with a constant input           | . 34 |

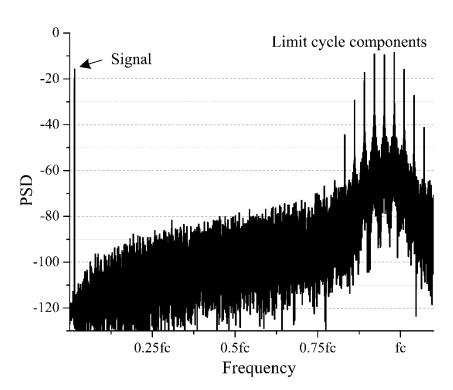

| Figure 2-9: Limit cycle frequency components with a small input signal ( $V = 0.3$ )                 | . 37 |

| Figure 2-10: Limit cycle frequency components with a large input signal ( $V = 0.8$ )                | . 38 |

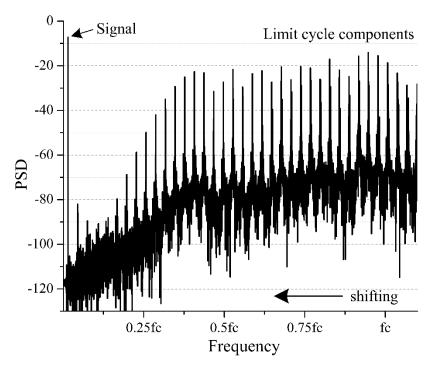

| Figure 2-11: Estimation for SFDR of ASDMs versus filter pole and normalized input voltage            |      |

| $(B = 3kHz, f_c = 200kHz)$                                                                           | . 40 |

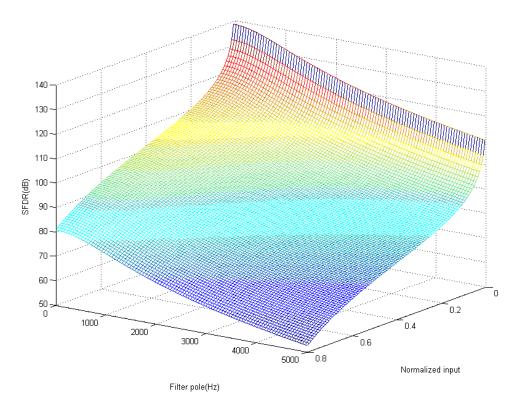

| Figure 2-12: Comparison of SFDR between the first order and second loop filters versus pole          |      |

| location ( $B = 3kHz$ , $V = 0.8$ , $f_c = 200kHz$ )                                                 | . 42 |

| Figure 2-13: Estimation for the achievable SFDR of the first order ASDM ( $V = 0.8$ , $f_{in} = B/3$ | ,    |

| $p_1 = 1kHz$ )                                                                                       | . 43 |

| Figure 2-14: System diagram of an asynchronous sigma delta modulator with propagation dela           |      |

|                                                                                                      | . 43 |

| Figure 2-15: Time diagram of asynchronous sigma delta modulators with propagation delay              | . 44 |

| Figure 2-16: Variation of the limit cycle frequency versus the propagation loop delay                | . 46 |

| Figure 2-17: Phenomenon of propagation delay                                                         | . 47 |

| Figure 2-18: SFDR of asynchronous sigma delta modulators with propagation loop delay                 | . 48 |

| Figure 2-19: Publications of ASDM during 40 years                                                    | . 49 |

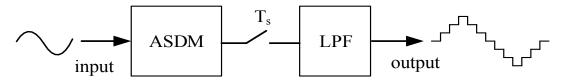

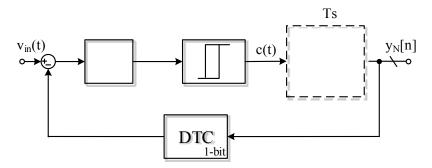

| Figure 3-1: System diagram of the ASDM with a sampler                                                | . 52 |

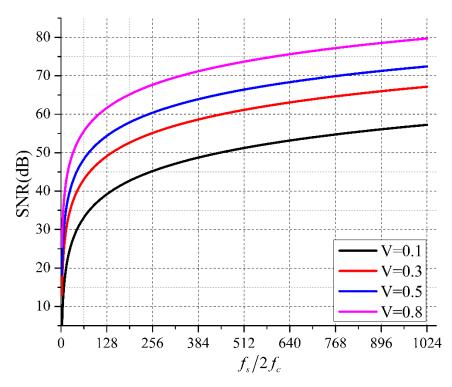

| Figure 3-2: Estimation for achieved SNR versus oversampling rate in different input amplitud         | le   |

| $(f_c/2B = 32, f_{in} = B/3)$                                                                        | . 52 |

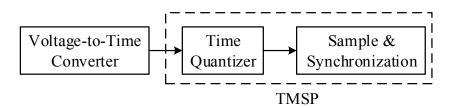

| Figure 3-3: System diagram of the analogue-to-digital of          | converter based on TMSP 5                       |

|-------------------------------------------------------------------|-------------------------------------------------|

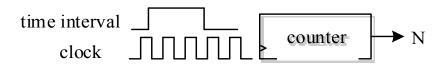

| Figure 3-4: Counter as a simple time-to-digital converte          | er5.                                            |

| Figure 3-5: Configuration of the flash time-to-digital co         | onverter 5                                      |

| Figure 3-6: (a) System diagram of the coarse-fine time-           | to-digital converter; (b) Timing diagram        |

| of the converter                                                  | 5                                               |

| Figure 3-7: Block diagram of the cyclic pulse-shrinking           | g TDC [77]5                                     |

| Figure 3-8: System diagram of the proposed ASDM dec               | coding circuit5                                 |

| Figure 3-9: Timing diagram of the proposed circuit                | 6                                               |

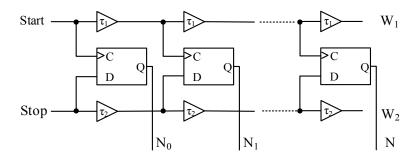

| Figure 3-10: Basic configuration of the vernier delay lin         | ne6                                             |

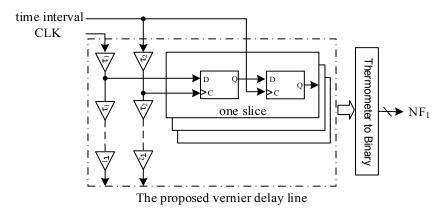

| Figure 3-11: Configuration of the proposed vernier dela           | ay line (each slice is one stage of the dela    |

| chains)                                                           | 6                                               |

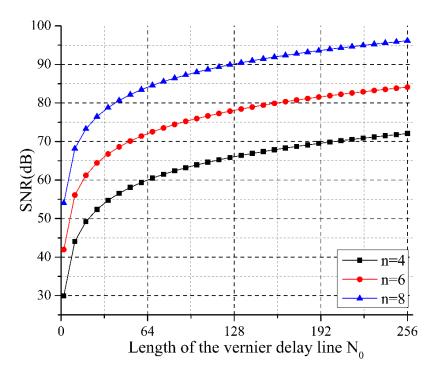

| Figure 3-12: Estimate of the achievable SNR of ASDM               | with the TDC for different numbers of           |

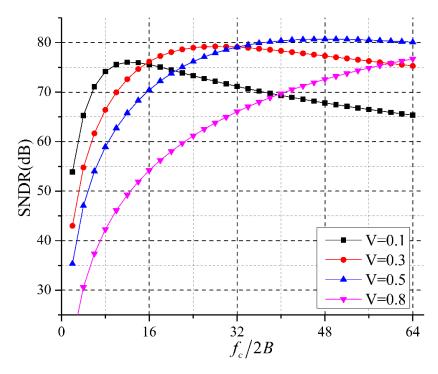

| bits of the counter                                               | 6                                               |

| Figure 3-13: Relationship between $f_c/2B$ and SNDR in            | n different modulation index ( $f_{in} = B/3$ , |

| $f_s = 10MHz$ $p_0 = 2kHz$ , $B = 3kHz$ and $\tau_{res} = 10ns$ ) | )6                                              |

| Figure 3-14: Illustration of the demodulation for the con         | nventional TDC6                                 |

| Figure 3-15: Operation of the proposed coarse-fine TD             | C6                                              |

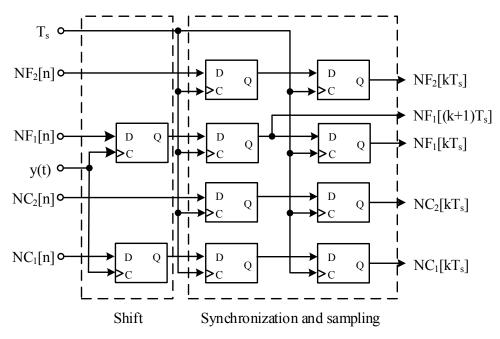

| Figure 3-16: Configuration of the proposed synchronize            | er6                                             |

| Figure 3-17: Configuration of the ASDM with noise sha             | aping7                                          |

| Figure 3-18: Relationship between SNDR and modulate               | ion index (with the same sample clock) 7        |

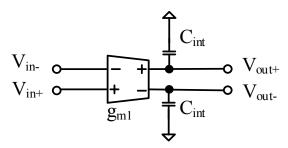

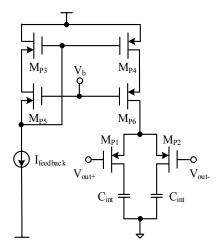

| Figure 3-19: Configuration of the Gm-C integrator                 | 7                                               |

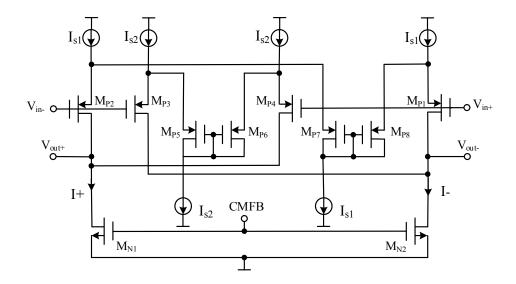

| Figure 3-20: Configuration of the proposed OTA                    | 7                                               |

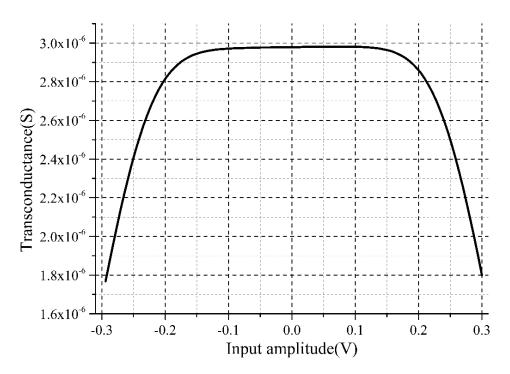

| Figure 3-21: Gm of the OTA versus input voltage                   | 7                                               |

| Figure 3-22: Schematic of the comparator with internal            | hysteresis                                      |

| Figure 3-23: Schematic of the feedback block                      | 7                                               |

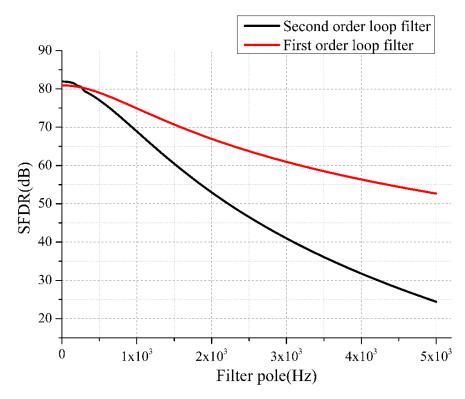

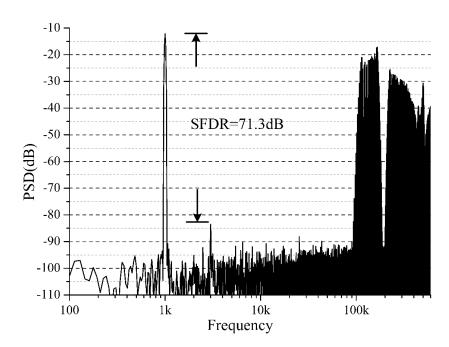

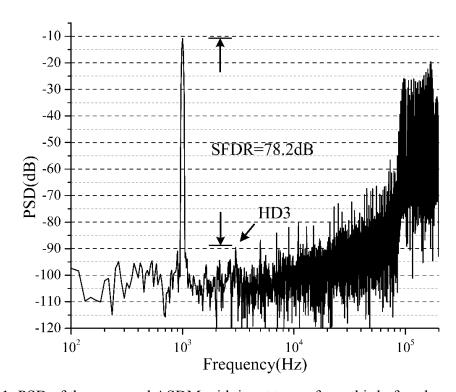

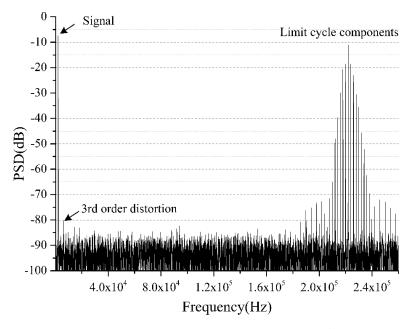

| Figure 3-24: PSD of the first order asynchronous sigma            | a delta modulator ( $f_{in} = 1kHz$ , and       |

| <i>V</i> = 0.8 )                                                  | 7                                               |

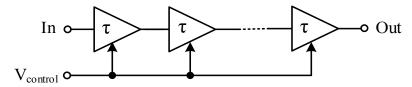

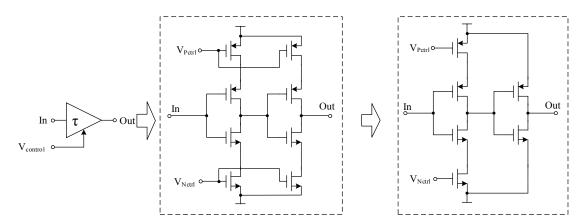

| Figure 3-25: Configuration of the voltage controlled de           | lay line8                                       |

| Figure 3-26: Schematic of the asymmetrical voltage con            | ntrolled delay element8                         |

| Figure 3-27: Schematic of the symmetric voltage control           | olled delay element                             |

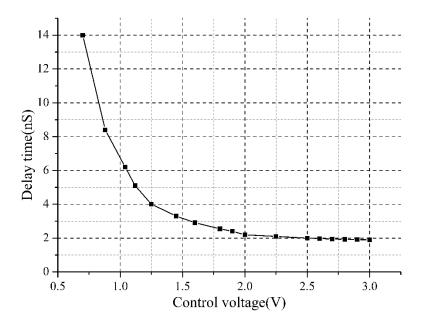

| Figure 3-28: Delay time versus the control voltage                                          | 82   |

|---------------------------------------------------------------------------------------------|------|

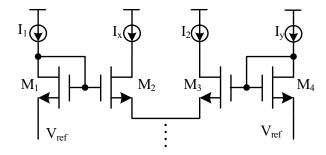

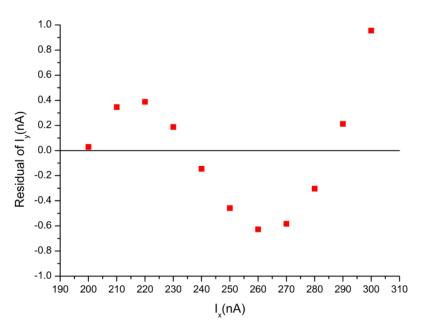

| Figure 3-29: Configuration of the translinear loop [84]                                     | 83   |

| Figure 3-30: Linearity of the translinear loop ( $I_0 = 200nA$ )                            | 83   |

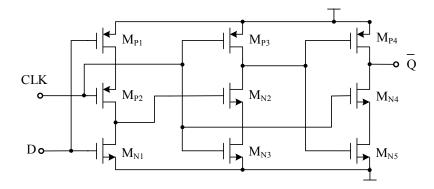

| Figure 3-31: Schematic of the TSPC D flip-flop                                              | 84   |

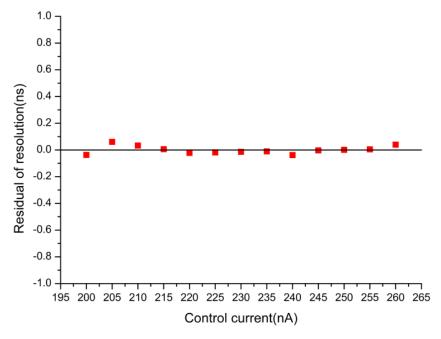

| Figure 3-32: Resolution error of the proposed vernier delay line                            | 85   |

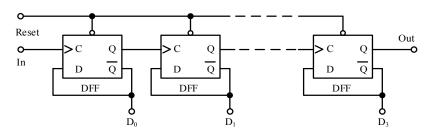

| Figure 3-33: Configuration of the coarse counter                                            | 85   |

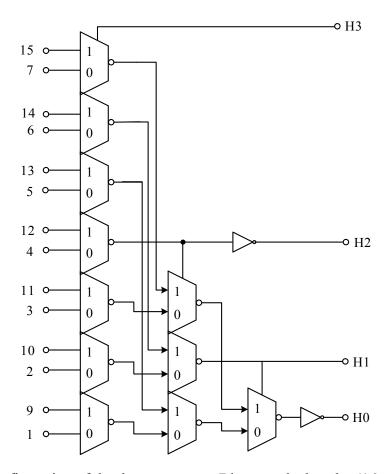

| Figure 3-34: Configuration of the thermometer to Binary code decoder (16-to-4 as example).  | 86   |

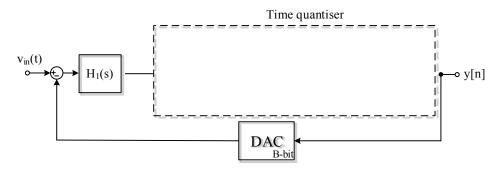

| Figure 4-1: System diagram of asynchronous sigma delta modulators with noise shaping        | 88   |

| Figure 4-2: Corresponding model with NRZ DAC                                                | 89   |

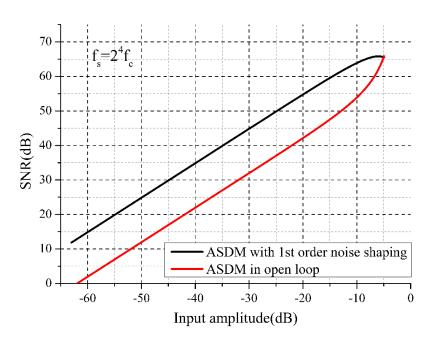

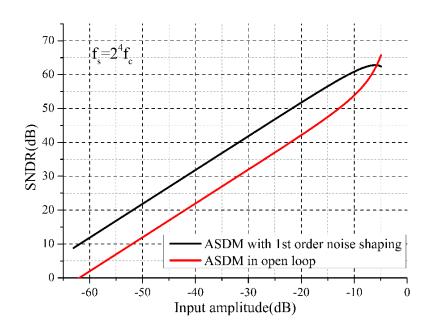

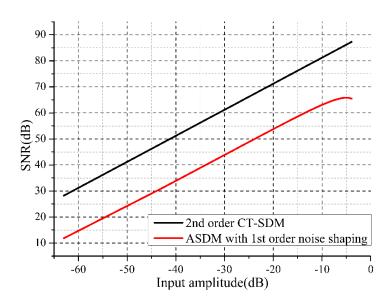

| Figure 4-3: SNR comparison between ASDMs with/without noise shaping                         | 90   |

| Figure 4-4: SNDR comparison between ASDMs with and without noise shaping ( $f_{in} = B/3$ ) | 91   |

| Figure 4-5: SNR comparison between the ASDM with 1st order noise shaping and the 2nd order  | er   |

| continuous-time-SDM                                                                         | 91   |

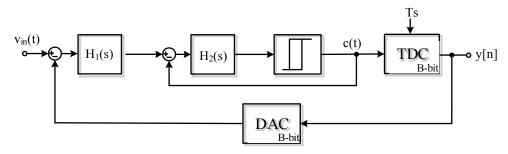

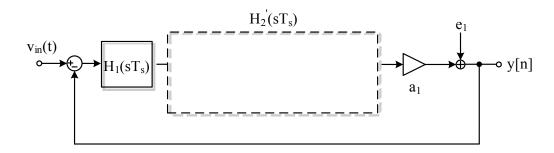

| Figure 4-6: Configuration of the proposed asynchronous sigma delta modulator                | 93   |

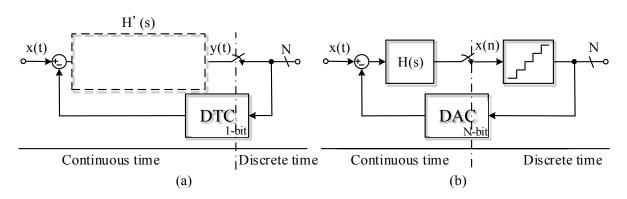

| Figure 4-7: Comparison of (a) the proposed ASDM and (b) the conventional CT-SDM             | 93   |

| Figure 4-8: Feedback loop of the proposed ASDM                                              | 94   |

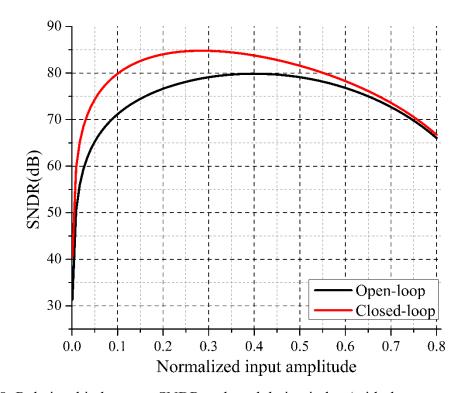

| Figure 4-9: Estimation of achieved SNDR of conventional and proposed ASDM                   | 100  |

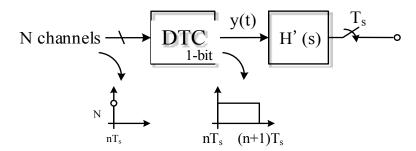

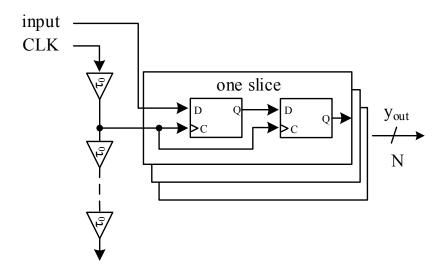

| Figure 4-10: Configuration of the proposed multi-poly phase sampler                         | 101  |

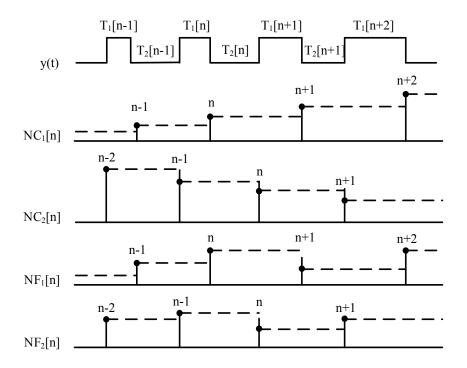

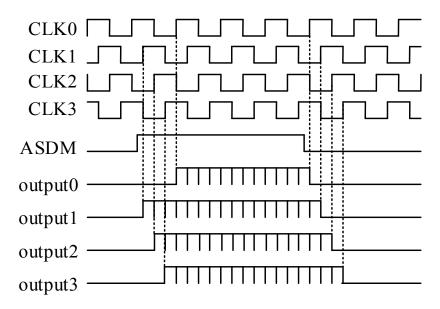

| Figure 4-11: Timing diagram for the poly-phase sampling ( $N = 4$ )                         | 102  |

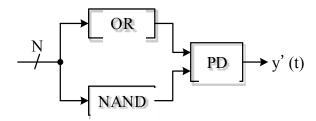

| Figure 4-12: Configuration of the time-to-digital converter.                                | 102  |

| Figure 4-13: Timing diagram for the time-to-digital converter                               | 102  |

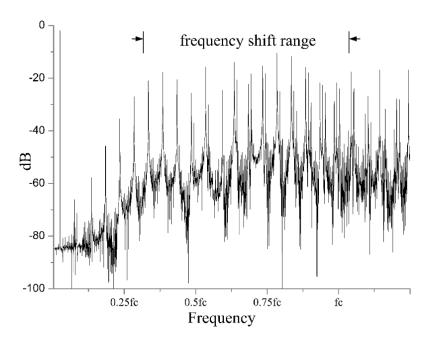

| Figure 4-14: PSD of ASDMs with 8 phases sampler with sampling clock of 2MHz, and            |      |

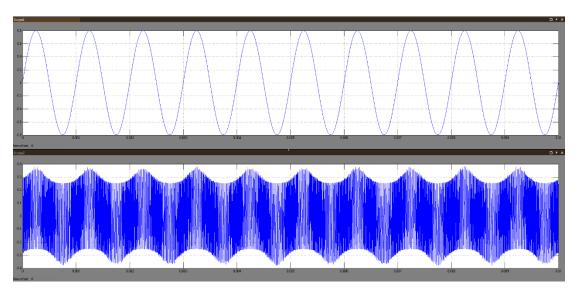

| following a 2 <sup>nd</sup> order LP filter (a) Conventional ASDM; (b) Proposed ASDM        | 103  |

| Figure 4-15: Clock jitter performance of the proposed ASDM                                  | 105  |

| Figure 4-16: Transconductance of the OTA versus input voltage                               | 106  |

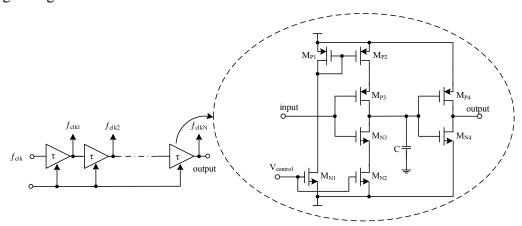

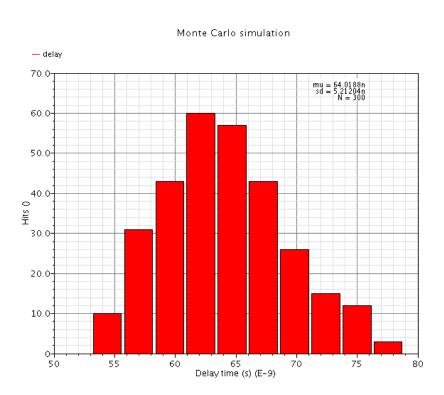

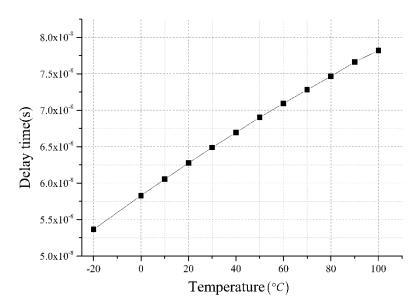

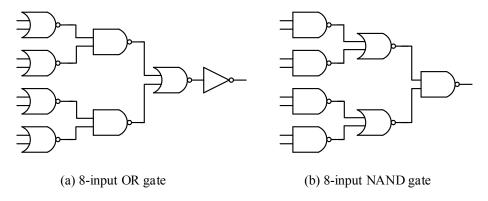

| Figure 4-17: Configuration of the delay chain.                                              | 107  |

| Figure 4-18: Monte Carlo simulation for one delay element                                   | 108  |

| Figure 4-19: Variation of the delay time versus temperature                                 | 109  |

| Figure 4-20: Configuration of the eight-input OR and NAND gates                             | 109  |

| Figure 4-21: PSD of the proposed ASDM with input tone of one third of analogue bandwidth    | .111 |

| Figure 5-1: Limit cycle components of asynchronous sigma delta modulators                   | 113  |

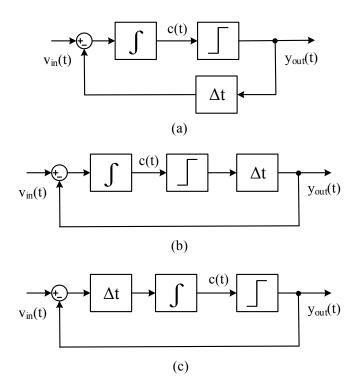

| Figure 5-2: Configurations of asynchronous sigma delta modulator (a) the delay cell in the               |      |

|----------------------------------------------------------------------------------------------------------|------|

| feedback loop [44]; (b) and (c) the delay cell in the feed-forward loop                                  | 114  |

| Figure 5-3: Timing diagram of the proposed asynchronous sigma delta modulator                            | 115  |

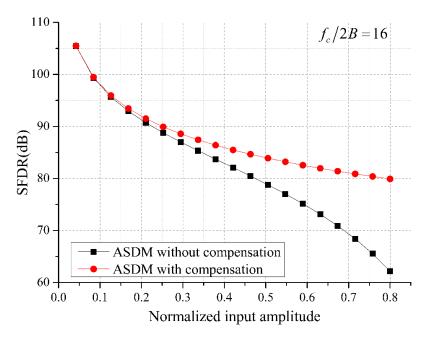

| Figure 5-4: SFDR of the conventional and proposed 1st order ASDMs versus normalized in                   | out  |

| amplitude ( $p_0/2\pi = f_{in} = B/3$ )                                                                  | 119  |

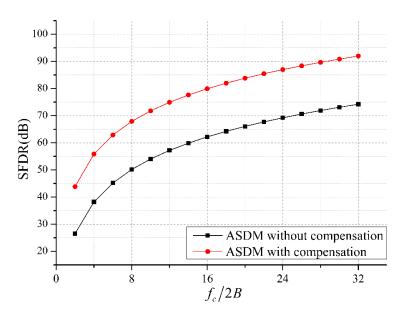

| Figure 5-5: Estimation for achieved SFDR versus $f_c/2B$ ( $V = 0.8$ and $p_1/2\pi = f_{in} = B/3$ )     | 120  |

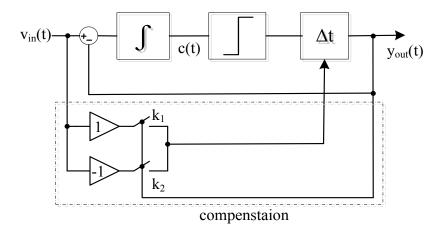

| Figure 5-6: System diagram of the first-order asynchronous sigma delta modulator with                    |      |

| frequency compensation                                                                                   | 121  |

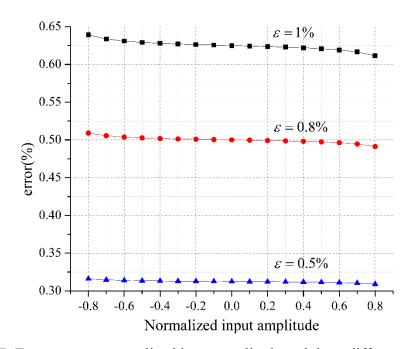

| Figure 5-7: Errors versus normalized input amplitude and three different value of $\varepsilon$          | 122  |

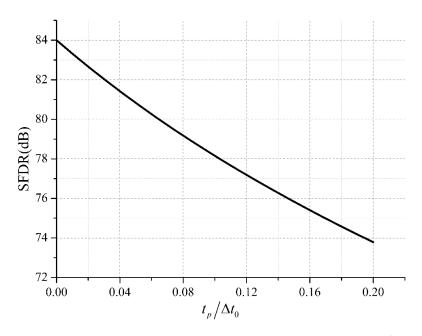

| Figure 5-8: Estimation for achieved SFDR versus $t_p/\Delta t_0$ with $V=0.8$ ( $f_c/2B=16$ , $f_{in}=B$ | 7/3, |

| $p_1/B = 1/6$ )                                                                                          | 123  |

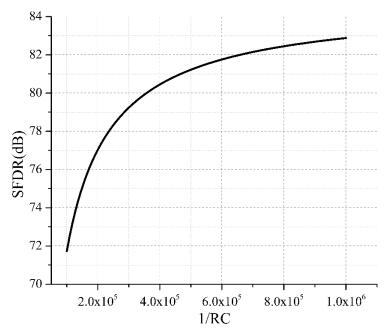

| Figure 5-9: Estimation for achieved SFDR versus integrator factor ( $f_c/2B = 16$ , $p_0/B = 1/6$        | I    |

| $f_{in} = B/3 \text{ and } b = 0.1)$                                                                     | 125  |

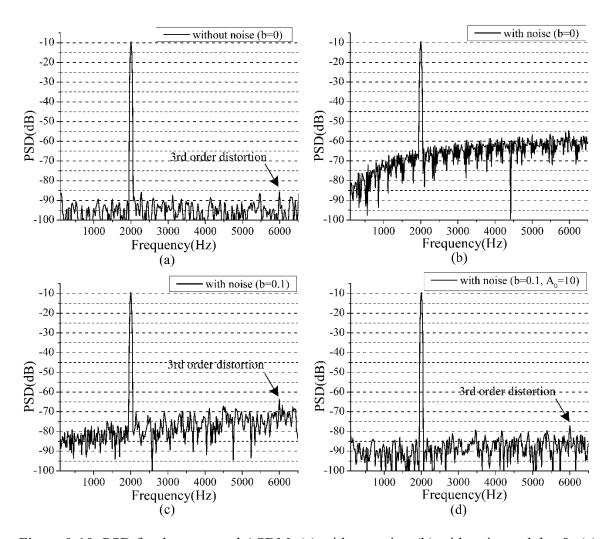

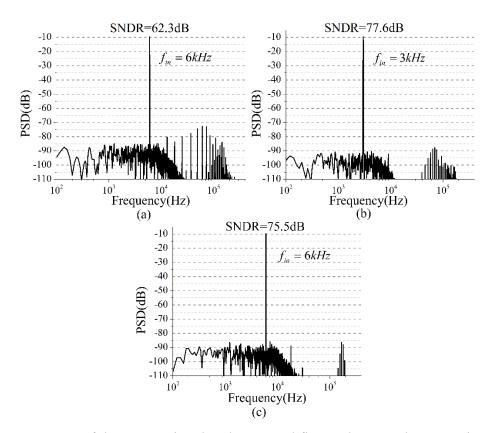

| Figure 5-10: PSD for the proposed ASDM: (a) without noise, (b) with noise and $b = 0$ , (c)              |      |

| $b = 0.1$ , (d) $b = 0.1$ and $A_0 = 10$ ( $f_s = 100MHz$ )                                              | 126  |

| Figure 5-11: SFDR versus the pole of the loop filter ( $f_c/2B=16$ )                                     | 127  |

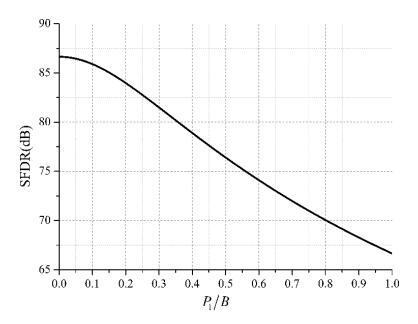

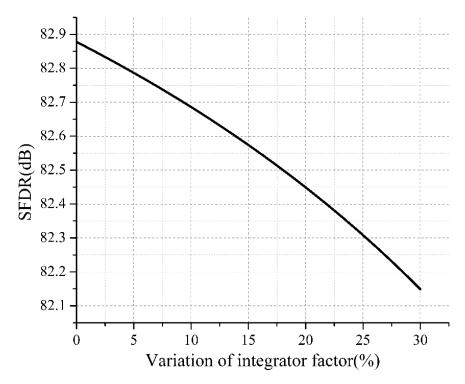

| Figure 5-12: Estimation for achieved SFDR versus variation of integrator factor ( $b = 0.1$ ,            |      |

| $f_c/2B = 16, V = 0.8$ and $f_{in} = B/3$ )                                                              | 128  |

| Figure 5-13: PSD of the conventional and proposed first-order asynchronous sigma delta                   |      |

| modulators: (a) and (b) are the conventional ASDM with 6kHz and 3kHz inputs,                             |      |

| respectively; (c) the proposed ASDM with 6kHz input                                                      | 129  |

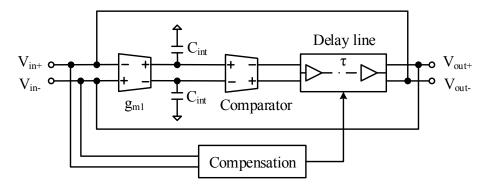

| Figure 5-14: Configuration of the proposed modulator                                                     | 130  |

| Figure 5-15: Schematic of the comparator implemented in the proposed modulator                           | 131  |

| Figure 5-16: Configuration of the compensation block                                                     | 132  |

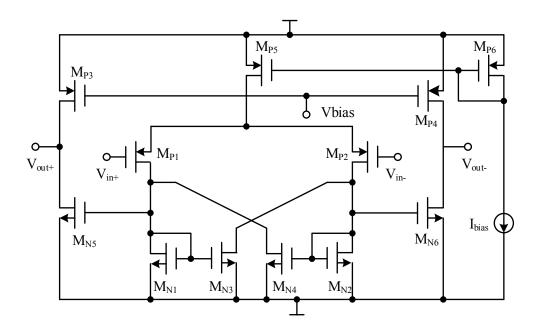

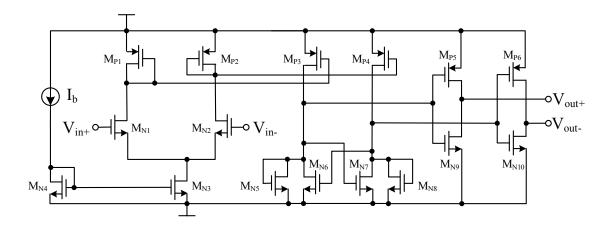

| Figure 5-17: Schematic of the voltage-to-current converter                                               | 133  |

| Figure 5-18: Schematic of the amplifier in the VCC                                                       | 133  |

| Figure 5-19: Shrinking/Stretching for the delay line: (a) Schematic of conventional delay ce             | lls; |

| (b) Timing diagram                                                                                       | 135  |

| Figure 5-20: Schematic of the proposed delay line by cascading two delay cells                           | 136  |

| Figure 5-21: Delay time of the rising and falling phase versus control voltage               | 137  |

|----------------------------------------------------------------------------------------------|------|

| Figure 5-22: Pulse width shrinking/stretching variation of the VCDL                          | 137  |

| Figure 5-23: Monte Carlo simulation of the delay line: (a) delay time for rising edge; (b) d | elay |

| time for falling edge                                                                        | 138  |

| Figure 5-24: Monte Carlo simulation for shrinking/stretching of the delay line               | 139  |

| Figure 5-25: Comparison of the output instantaneous frequency between the conventional       |      |

| ASDM and the proposed one                                                                    | 140  |

| Figure 5-26: Stability of the frequency in the proposed ASDM                                 | 140  |

| Figure 5-27: Normalized error of the duty cycle of the proposed ASDM                         | 141  |

| Figure 5-28: PSD of the proposed ASDM ( $f_c/2B=16$ )                                        | 141  |

|                                                                                              |      |

# **List of Symbols**

A list of the major symbols, notations and abbreviations with their definitions are as follows:

|                        | Absolute value                     |

|------------------------|------------------------------------|

| $\otimes$              | Convolution                        |

| Re                     | Real part of a complex number      |

| Im                     | Imaginary part of a complex number |

| $FT(\ )$               | Fourier transfer function          |

| В                      | Signal bandwidth                   |

| $f_0$                  | Output instantaneous frequency     |

| $f_c$                  | Limit cycle frequency              |

| $T_s$                  | Period of sample clock             |

| $T_{ref}$              | Period of reference clock          |

| $\mu$                  | Input signal frequency             |

| τ                      | Delay time of the delay line       |

| $T_{DR}$               | Dynamic range of the delay line    |

| $A_0$                  | Open loop gain                     |

| $\Delta 	au$           | Propagation delay time             |

| $e_{_{1}}/\varepsilon$ | Quantisation error                 |

| L                      | Order of the loop filter           |

| V                      | Normalized input signal amplitude  |

| α                      | Duty cycle of the data signal      |

| F                      | Carrier-to-bandwidth ratio         |

| NC                     | Output of the coarse measurement   |

| NF                     | Output of the fine measurement     |

| b                      | Hysteresis of the comparator       |

| p                      | Pole frequency of the loop filter  |

k = 1/RC Integration gain

$\Delta_3$  /HD<sub>3</sub> The third order distortion

gm Transconductance

$V_{fb}$  Amplitude of the feedback signal

$I_{bias}$  Bias current

I Current

$V_{control}$  Control voltage of the delay line

$C_{ox}$  Oxide capacitance of the gate-to-body per unit area

$\mu_n$  Electron mobility in the induced n channel

$\mu_p$  Electron mobility in the induced p channel

Δ Minimum quantisation step

$\Delta t_0$  Delay time of the delay line

SC Switch capacitor

STF Signal transfer function

*NTF* Noise transfer function

SNR Signal-to-noise ratio

*SQNR* Signal-to-quantisation noise ratio

SFDR Spurious-free dynamic range

SNDR Signal-to-noise and distortion ratio

OSR Oversampling ratio

ADC Analogue-to-digital converter

DAC Digital-to-analogue converter

SDM Sigma delta modulator

PWM Pulse width modulator

*DT – SDM* Discrete-time sigma delta modulator

*CT – SDM* Continuous-time sigma delta modulator

ASDM Asynchronous sigma delta modulator

NTZ Non-return-to-zero

*RZ* Return-to-zero

HZ Hold-return-to-zero

VDL Vernier delay line

VCDL Voltage controlled delay line

TDC Time-to-digital converter

TL Translinear loop

DTC Tine-to-digital converter

PLL Phase locked loop

DLL Delay locked loop

LPF Low pass filter

TMSP Time-mode signal processing

INL Integral non-linearity

DNL Differential non-linearity

LSB Least significant bit

OTA Operational transconductance amplifier

Gm-C Transconductor-capacitor circuit

### Introduction

#### 1.1 Motivation

Despite its long history, the sigma delta modulator remains one of the most popular data converter circuits. Conventionally, sigma delta modulators are widely implemented in low-speed, high-resolution applications. Low power consumption is a particularly important feature in portable applications, leading to long battery life. Consequently, power-efficient architectures such as continuous-time sigma delta modulators have been attracted more attention in recent years.

Continuous-time sigma delta modulators use a cascade of several loop filters to establish a high order noise shaping, so as to realize a high resolution. A single-bit digital-to-time converter (DAC) inherently linear, is implemented in the feedback loop for reasons of circuit simplicity and low power consumption. However, the single-bit quantizer in the forward path will raise stability issues in high order modulators [1]. To solve this issue, a multi-bit internal quantizer is often used to obtain sufficient gain for implementing a stable sigma delta loop filter. This creates another issue: An equivalent high resolution DAC is required in the feedback loop, which increases the complexity of the modulator and the power consumption.

Continuous-time sigma delta modulators require a high sampling frequency to obtain an equivalent over-sampling ratio, in order to improve performance. High sampling frequency not only means increased power dissipation of the clock and sampler, but also increases the design and simulation time and the power consumption of the wideband loop and decimation filters. All this limits sigma delta modulators to ultra-low power applications, such as biomedical and environmental sensors. Other design issues around continuous-time sigma delta modulators include propagation delay and sensitivity to clock jitter. Propagation delay undermines dynamic stability and introduces the need for compensation.

In fact, there does exist another type of sigma delta modulators, named asynchronous sigma delta modulators (ASDM), which has potential properties to solve this issue. ASDMs can be considered as a special type of continuous-time sigma delta modulators. Unfortunately, in current CMOS technology, ASDMs are difficult to implement in data conversion, because of some critical issues. Most significant drawback is the absence of effective circuit to digitise the modulated signal. Other issues which can be resolved including the signal bandwidth which is limited by the limit cycle components and lacking of shaping for quantisation errors. This thesis presents solutions to solve these issues.

#### 1.2 Objectives

This thesis presents studies of the asynchronous sigma delta modulator and proposes solutions to their limitations.

- 1. Improve a decoding scheme for ASDMs. In the first instance, I noticed that conventional decoding schemes for asynchronous sigma delta modulators limit input dynamic range of modulators, and always requires a high speed sampling clock. This is because conventional decoding schemes can only measure the time interval not the duty cycle of the square wave, and they always use a fast sample to digital the location of the time interval rather than its exact the time value. In order to obtain the duty cycle, two decoding schemes are required to measure both the pulse width and the period, which doubles the chip area and power dissipation. To solve this issue, I introduce a novel decoding scheme for asynchronous sigma delta modulators, which can convert the duty cycle of modulated square wave into digital signals directly. The proposed decoding scheme is realized by a special coarse-fine time-to-digital converter (TDC), and it can measure the duty cycle of the data signal without knowing its instantaneous period.

- 2. Improve the architecture of ASDMs to introduce noise shaping. I found that the conventional architecture of asynchronous sigma delta modulators with noise shaping with additional loop filter and feedback loop is not efficient. Because the loop filter in the ASDM does not contribute to shape the quantisation errors. And it requires a high resolution digital-to-analogue converter (DAC) in the feedback loop, which increases the design challenge and the complexity of the circuit. Compared with the same system order

synchronous-time sigma delta modulator, the conventional architecture has poorer performance.

3. Improve the architecture of ASDMs to minimize effects of limit cycle components. Finally, I noticed that the limit cycle components of asynchronous sigma delta modulators significantly limit the signal bandwidth of modulators, and it also requires a powerful decimation filter to supply a high attenuation for out-band components. This issue makes ASDM difficult to implement. To overcome this issue, another architecture of ASDMs is implemented, where the limit cycle frequency is determined by the delay time of a delay cell. It give an opportunity to stable the frequency of the output by controlling the delay time of the delay cell. The proposed ASDM works as an ideal pulse width modulator (PWM), which increases design space of decoding circuits, and reduces the requirement of the decimation.

#### 1.3 Outline of this thesis

The thesis is organized in 6 chapters, including the present one. A brief summary of each chapter is given below.

Chapter 2 provides a brief literature review of sigma delta modulators in past five years. A detailed system analysis of asynchronous sigma delta modulators is presented, including fundamental analysis, noise performance and non-idealises.

Chapter 3 presents the implementation of an asynchronous sigma delta modulator with a novel decoding circuit. It discusses the issues of conventional decoding circuits, and introduces a new decoding methodology to overcome these issues. It also presents the architecture of the proposed modulator and decoding circuit in some details, along with simulation results.

Chapter 4 introduces a novel architecture of asynchronous sigma delta modulators with noise shaping. It solves the issues of conventional architectures of asynchronous sigma delta modulators with noise shaping, and presents the details of system analysis and circuits design. The results of the system analysis are illustrated by transistor level simulation results of modulator circuits.

Chapter 5 presents improvements of the asynchronous sigma delta modulator leading to a constant output frequency. This is achieved by the introduction of a compensation block. The methodology of frequency compensation is presented in detail. This chapter concludes with transistor-level simulation results of the entire modulator circuits in an AMS  $0.35 \mu m$  CMOS process.

Chapter 6 presents some concluding remarks, outlines the limitations of the thesis and discusses some potential directions for future research.

### Sigma Delta Modulation Fundamentals

#### 1.4 Introduction

Analogue-to-Digital converters (ADCs) are key building blocks in electronic systems, including as audio, communication, industry measurement and sensor interfaces. Together with digital-toanalogue converters (DACs), they interface analogue real world signals to the digital signal processing system. Application requirements, such as speed, resolution and power consumption, dictate specific ADC architectures to optimise trade-off between power, speed and performance. The sigma delta analogue-to-digital converters are preferred in high-resolution, low-speed applications. Sigma delta converters use oversampling, error processing, and feedback to improve the resolution of the quantiser. In other words many samples of the input signal taken at a high rate are used to produce an output signal at the Nyquist rate. Sigma delta converters are feedback devices operating in closed-loop mode; this makes them tolerant to some analogue imperfections, including offset and mismatch. Additionally, signal processing in a sigma delta analogue-to-digital converter is partitioned between analogue and digital sub-sections; analogue filtering is employed for quantisation error rejection from the signal band, while digital filtering is used to increase the effective resolution by eliminating the out of band quantisation noise [2]. The single-bit sigma delta converter is inherently monotonic and requires no laser trimming [1]. It also lends itself to low cost CMOS foundry processes because of the digitally intensive nature of the architecture. This chapter will present the fundamentals of both synchronous and asynchronous sigma delta modulators.

#### 1.5 Synchronous sigma delta modulators

#### 1.5.1 Discrete-time sigma delta modulator

Discrete-time sigma delta analogue-to-digital converters make use of two basic ideas: oversampling and noise shaping, to decrease the quantisation error power within the signal band and increase the resolution of the conversion. The basic system diagram of a discrete-time sigma delta analogue-to-digital converter is shown in Fig. 2-1. It includes three basic components: an

anti-aliasing filter, a discrete-time sigma delta modulator and a decimator (a digital filter and a down-sampler).

Figure 0-1: Block diagram of a discrete-time sigma delta analogue-to-digital converter

The function of the anti-aliasing filter is to attenuate the out-band components of the input signal so as to avoid aliasing during sampling process. The basic fundamental operations of discrete-time sigma delta modulators is to enclose a simple quantiser in a feedback loop in order to shape the spectrum of both the input signal and the quantisation noise. Typically, the signal is low passed, while the baseband noise is shifted to higher frequencies, and can be suppressed by the filter. This process, known as noise shaping, makes sigma delta modulators much more robust than other analogue-to-digital converters. The output signal of the modulator is fed into a digital filter which attenuates the out-band frequency components and noise. Finally the output signal is down-sampled to the Nyquist rate.

The transfer function of the modulator can be obtained in the z-domain by:

$$Y(z) = STF(z)X(z) + NTF(z)E(z)$$

(2-1)

Where X(z) and E(z) are the z-transform of the input signal and the quantisation error, respectively; STF(z) and NTF(z) are the respective transfer functions for the input signal and quantisation error, which are determined by the architecture implemented by the modulator. According to Fig. 2-1, they are given by

$$\begin{cases}

STF(z) = \frac{H(z)}{H(z)+1} \\

NTF(z) = \frac{1}{H(z)+1}

\end{cases} (2-2)$$

Where H(z) is the loop filter transfer function. By implementing a simple ideal loop filter:

$$H(z) = \frac{z^{-1}}{1 - z^{-1}} \tag{2-3}$$

Eq. (2-1) can be extended to an  $L^{th}$  order system yields:

$$Y(z) = z^{-L}X(z) + (1 - z^{-L})E(z)$$

(2-4)

Ideally, the dynamic range of the  $L^{th}$  order sigma delta modulator is:

$$DR \approx 6.02N + 1.76 + 10\log_{10}\left(\frac{2L+1}{\pi^{2L}}\right) + (2L+1)10\log_{10}(OSR)$$

(2-5)

Where  $OSR = f_s/2B$  is the oversampling ratio; N is the bit of the quantiser.

The dynamic range of the modulator will, in general, be limited by quantisation noise and circuit imperfections.

#### 1.5.2 Continuous-time sigma delta modulator

The first recognizable sigma delta modulator, introduced in 1962, was actually implemented as a continuous-time circuit [3]. However, because of the excellent performance of switched-capacitor circuits, most sigma delta modulators are implemented as the discrete-time mode. Switched-capacitor sigma delta modulators are still very popular in middle frequency applications because of their insensitivity to signal waveform. As the time constants of switched-capacitor integrators scale with sampling frequency, switched capacitor modulator circuits allow for greater system flexibility [4].

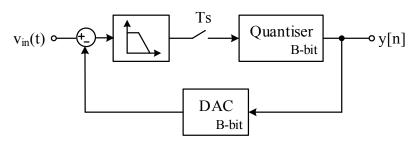

However, continuous-time sigma delta modulators are attracting attention once again thanks to the increasing demand for lower power circuits. Continuous time modulators have a unique benefit, namely the inherent anti-aliasing filtering offered by the continuous-time loop filter. Continuous-time loop filters are much faster than their discrete-time counterparts, making continuous-time sigma delta modulators popular in high-speed analogue-to-digital converters. The configuration of a basic continuous-time sigma delta modulator is shown in Fig. 2-2.

Figure 0-2: Basic configuration of the continuous-time sigma delta modulator with multi-bit quantiser

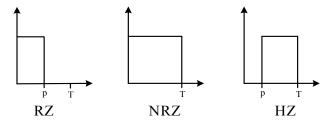

The architecture of any arbitrary continuous-time sigma delta modulator can be generated by applying a discrete-time to continuous-time transformation to an original discrete-time sigma delta modulator. Depending on the shape of the digital-to-analogue converter impulse response, there are different ways to realizing such a discrete-time to continuous-time transformation. Conventionally, there are three types of conventional digital-to-analogue waveforms: rectangular, triangular and exponential. The rectangular waveforms are easier to implement, while the less popular triangular and exponential waveforms result in better jitter tolerance [5]. Rectangular waveforms include three formats: non-return-to-zero (NRZ), return-to-zero (RZ) and hold-return-to-zero (HZ), as shown in Fig. 2-3. The time definition of these waveforms  $R_p(t)$  based on the step function u(t) is shown as follows:

$$\begin{cases}

R_{p}(t)\big|_{NRZ} = u(t) - u(t - T) \\

R_{p}(t)\big|_{RZ} = u(t) - u(t - p) \\

R_{p}(t)\big|_{HZ} = u(t - p) - u(t - T)

\end{cases}$$

(2-6)

And the equivalent s-domain forms of eq. (2-7) is:

$$\begin{cases}

NRZ(s) = \frac{1 - e^{-sT}}{s} \\

RZ(s) = \frac{1 - e^{-sp}}{s} \\

HZ(s) = \frac{e^{-sp} - e^{-sT}}{s}

\end{cases}$$

(2-7)

Figure 0-3: Digital-to-analogue converter wave forms for RZ, NRZ, and HZ

Equivalent discrete-time to continuous-time conversions for rectangular digital-to-analogue converter waveforms are listed in Table 2-1.

Table 0-1: Example of z-domain and s-domain sigma delta modulator transformation

| Loop filters | 1st order low-pass        | 2 <sup>nd</sup> order low-pass                                |

|--------------|---------------------------|---------------------------------------------------------------|

| H(z)         | $\frac{z^{-1}}{1-z^{-1}}$ | $\frac{z^{-1}\left(2-z^{-1}\right)}{\left(1-z^{-1}\right)^2}$ |

| H(s)(RZ)     | $\frac{2}{Ts}$            | $\frac{2+2.5Ts}{\left(Ts\right)^2}$                           |

| H(s)(NRZ)    | $\frac{1}{Ts}$            | $\frac{1+1.5Ts}{\left(Ts\right)^2}$                           |

Continuous-time sigma delta modulators have several critical limitations. The first one is related to the excess loop delay. In practice, there exists a certain delay between the quantiser sampling event and the DAC output, caused by the imperfection of circuits implemented in the modulator, such as the finite open loop gain and bandwidth of the loop filter, the propagation delay time in comparator, etc. This delay cause instability of the modulator loop. In intuitive terms, if the DAC feedback waveform is not contained in one sampling period due to the excess loop delay, the effective order of the loop filter is larger than desired; the loop poles move towards the unite circle, and the modulator stability becomes poor. Moreover, the excess loop delay can elevate the quantisation noise floor by degrading the noise transfer function at low-frequencies.

Continuous time sigma delta modulators are also more sensitive to the clock jitter than discrete-time sigma delta modulators; the internal clock not only controls the comparison instant, but also controls the rising and falling edges of the digital-to-analogue converter output. As a result, clock jitter errors are directly added to the input signal. The effect of clock jitter in continuous-time sigma delta modulators has been extensively analysed in the literatures [6-8]. K. Reddy and S. Pavan's work showed that the jitter induced noise in modulators with NRZ feedback is predominantly determined by the out-band behaviour of the NTF, thus more aggressive noise shaping exacerbates the jitter sensitivity.

Many authors have presented solutions to these issues. However, they all focus on the detailed circuit design and some compensation techniques [9-12], which increase the challenge of design, complex of the circuits, and the power dissipation as well. The comparison between DT-SDM and CT-SDM is shown in Table 2-2.

Table 0-2: Comparison between DT-SDM and CT-SDM

|               | DT-SDM                                                      | CT-SDM                            |

|---------------|-------------------------------------------------------------|-----------------------------------|

| Common        | Synchronous modulator                                       |                                   |

|               | Noise shaping and over-sampling                             |                                   |

|               | • High order system (at least 2 <sup>nd</sup> order system) |                                   |

| Advantages    | High resolution                                             | Inherent anti-aliasing filter     |

|               | Developed technology                                        | High conversion speed             |

| Disadvantages | Require pre anti-aliasing filter                            | Sensitive to clock jitter         |

|               | Low conversion speed                                        | • Excess loop delay (instability) |

• Instability (high order system)

#### 1.6 State of the art for the synchronous sigma delta modulator

With the exception of a few milestone works, referenced for completeness, a literature survey on recently published synchronous sigma delta modulators is summarized in Table 2-2. Discrete-time sigma delta modulators are implemented by switched-capacitor or switched-current techniques; continuous-time sigma delta modulators are often realized by active-RC or Gm-C techniques. The signal bandwidth, signal-to-noise ratio (SNR), signal-to-noise and distortion ratio (SNDR), and power consumption are key performance metrics that can be used for comparing different designs. Low pass sigma delta modulators are evaluated by two figures-of-merits, namely:

$$FOM_{W} = \frac{P}{2B \times 2^{ENOB}} \tag{2-8}$$

$$FOM_{S} = SNDR + 10\log\left(\frac{B}{p}\right) \tag{2-9}$$

FOM<sub>W</sub> emphasizes power consumption, whereas FOM<sub>S</sub> emphasizes resolution. Better performance of sigma delta modulators is indicated by smaller FOM<sub>w</sub> and larger FOM<sub>S</sub> values.

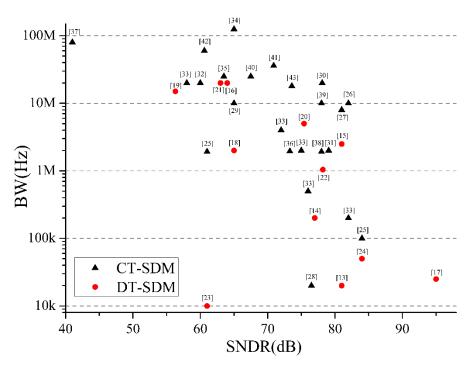

The data in Table 2-3 clearly shows that current trend is towards continuous-time sigma delta modulators; an increasing number of published sigma delta modulators are based on the continuous-time approach. In order to form an idea of current design trends, and to compare the potentials of discrete-time and continuous-time implementation, a survey of design approaches is presented here. The survey covers publications in the IEEE International Solid State Circuits Conference (ISSCC) and the IEEE VLSI Conference from 2008 to 2013. Fig. 2-4 shows the Signal-to-Noise-and Distortion (SNDR) versus signal bandwidth of discrete-time and continuous-time implementations. Continuous-time circuits mostly cover the high frequency applications. The higher dynamic range is mostly occupied by low signal bandwidth, discrete-time implementations. A survey of power consumption versus Nyquist output frequency is presented in Fig. 2-5. Note that the continuous-time implementations, even in high frequency applications, still show a lower

power consumption than their discrete-time counterparts. A final comparison is shown in Fig. 2-6 where we can observe that continuous-time converters have better  $FOM_S$  than their discrete-time counterparts.

Figure 0-4: SNDR and signal bandwidth of recently published synchronous sigma delta modulators

Figure 0-5: FOMw versus Nyquist output frequency

Figure 0-6: FOM<sub>S</sub> versus Nyquist output frequency

Table 0-3: State of the art of synchronous sigma delta modulators

| Discrete-time sigma delta modulators   |            |         |         |     |       |         |                |       |

|----------------------------------------|------------|---------|---------|-----|-------|---------|----------------|-------|

| Year                                   | Technology | BW      | Fs      | OSR | SNDR  | Power   | $FOM_W$        | FOMs  |

|                                        | (um)       | (Hz)    | (Hz)    |     | (dB)  | (mW)    | (fJ/conv-step) | (dB)  |

| 2008[13]                               | 0.18       | 2.00E+4 | 4.00E+6 | 100 | 81.0  | 3.60E-2 | 98.1           | 168.4 |

| 2008[14]                               | 0.065      | 2.00E+5 | 1.50E+8 | 375 | 77.0  | 9.50E-1 | 410.5          | 160.2 |

| 2008[15]                               | 0.18       | 2.50E+6 | 6.00E+7 | 12  | 83.0  | 15.0    | 327.1          | 163.2 |

| 2008[16]                               | 0.09       | 2.00E+7 | 4.20E+8 | 11  | 72.0  | 27.9    | 538.6          | 152.6 |

| 2008[17]                               | 0.18       | 2.50E+4 | 5.00E+6 | 100 | 100.0 | 8.70E-1 | 378.5          | 169.6 |

| 2009[18]                               | 0.09       | 2.00E+6 | 3.20E+8 | 80  | 65    | 6.83    | 1175.0         | 149.7 |

| 2009[19]                               | 0.045      | 1.50E+7 | 1.50E+9 | 50  | 56.3  | 9.00    | 562.1          | 148.5 |

| 2009[20]                               | 0.18       | 5.00E+6 | 8.00E+7 | 8   | 75.4  | 36.0    | 748.1          | 156.8 |

| 2011[21]                               | 0.032      | 2.00E+7 | 4.00E+8 | 10  | 63.0  | 28.0    | 606.4          | 151.5 |

| 2011[22]                               | 0.18       | 1.04E+6 | 5.00E+7 | 24  | 78.2  | 2.90    | 209.5          | 163.8 |

| 2011[23]                               | 0.13       | 1.00E+4 | 1.40E+6 | 70  | 61.0  | 7.50E-3 | 409.0          | 152.2 |

| 2011[24]                               | 0.18       | 5.00E+4 | 1.60E+6 | 16  | 84.0  | 1.40E-1 | 108.1          | 169.5 |

| Continuous-time sigma delta modulators |            |         |         |     |       |         |                |       |

| Year                                   | Technology | BW      | Fs      | OSR | SNDR  | Power   | $FOM_W$        | FOMs  |

|                                        | (um)       | (Hz)    | (Hz)    |     | (dB)  | (mW)    | (fJ/conv-step) | (dB)  |

| 2008[25]                               | 0.065      | 1.00E+5 | 2.60E+7 | 130 | 84.0  | 2.10    | 810.5          | 160.8 |

| 2008[25]                               | 0.065      | 1.92E+6 | 6.24E+7 | 16  | 61.0  | 3.20    | 908.9          | 148.8 |

| 2008[26]                               | 0.18       | 1.00E+7 | 6.40E+8 | 32  | 82.0  | 100     | 485.9          | 162.0 |

| 2008[27]                               | 0.065      | 8.00E+6 | 2.56E+8 | 16  | 81.0  | 50.0    | 340.8          | 163.0 |

| 2008[28]                               | 0.045      | 2.00E+4 | 1.20E+7 | 300 | 76.5  | 1.20    | 5492.2         | 148.7 |

| 2009[29]                               | 0.09       | 1.00E+7 | 6.40E+8 | 32  | 65.0  | 6.80    | 234.0          | 156.7 |

| 2009[30]                               | 0.13       | 2.00E+7 | 9.00E+8 | 23  | 78.1  | 87.0    | 331.2          | 161.7 |

| 2009[31]                               | 0.065      | 2.00E+6 | 1.28E+8 | 32  | 79.1  | 4.52    | 153.9          | 165.5 |

| 2009[32]                               | 0.065      | 2.00E+7 | 2.50E+8 | 6   | 60.0  | 10.5    | 321.2          | 152.8 |

| 2010[33]                               | 0.09       | 2.00E+5 | 5.12E+7 | 128 | 82.0  | 2.80    | 680.3          | 160.5 |

| GSM mode                               |            |         |         |     |       |         |                |       |

| 2010[33]                               | 0.09       | 5.00E+5 | 9.60E+7 | 96  | 78    | 2.60    | 504.2          | 158.8 |

| BT mode                                |            |         |         |     |       |         |                |       |

| 2010[33]                               | 0.09       | 2.00E+6 | 1.28E+8 | 32  | 75    | 3.60    | 195.8          | 162.4 |

| UMTS mode                              |            |         |         |     |       |         |                |       |

| 2010[33]<br>DVB-H mode | 0.09  | 4.00E+6 | 1.92E+8 | 24 | 72   | 4.90 | 188.3   | 161.1 |

|------------------------|-------|---------|---------|----|------|------|---------|-------|

| 2010[33]               | 0.09  | 2.00E+7 | 6.40E+8 | 16 | 58   | 8.50 | 327.4   | 151.7 |

| WLAN mode              |       |         |         |    |      |      |         |       |

| 2011[34]               | 0.045 | 1.25E+8 | 4.00E+9 | 16 | 65.0 | 256  | 704.7   | 151.9 |

| 2011[35]               | 0.09  | 2.50E+7 | 5.00E+8 | 10 | 63.5 | 8.00 | 130.9   | 158.4 |

| 2011[36]               | 0.065 | 1.95E+6 | 1.25E+8 | 32 | 73.3 | 8.55 | 580.2   | 156.9 |

| 2011[37]               | 0.04  | 8.00E+7 | 8.88E+9 | 56 | 41.0 | 164  | 11148.1 | 127.9 |

| 2011[38]               | 0.04  | 1.92E+6 | 2.46E+8 | 64 | 78.0 | 2.80 | 112.3   | 166.4 |

| 2012[39]               | 0.09  | 1.00E+7 | 6.00E+8 | 30 | 78.0 | 16.0 | 123.2   | 166.0 |

| 2012[40]               | 0.09  | 2.50E+7 | 5.00E+8 | 10 | 67.5 | 8.50 | 87.7    | 162.2 |

| 2012[41]               | 0.09  | 3.60E+7 | 3.60E+9 | 50 | 70.9 | 15.0 | 72.7    | 164.7 |

| 2012[42]               | 0.045 | 6.00E+7 | 6.00E+9 | 50 | 60.6 | 20.0 | 190.4   | 155.4 |

| 2013[43]               | 0.028 | 1.80E+7 | 6.40E+8 | 18 | 73.6 | 3.90 | 27.7    | 170.2 |

#### 1.7 Asynchronous sigma delta modulators

A new type of sigma delta modulators, originally introduced by Kikkert [44], has recently attracted attention. This type of modulator was forgotten for many years until interest revived due to its perceived potential for high frequency and low power application in the absence of a fast system clock. The dynamics of asynchronous sigma delta modulators were studied in detail by Roza and Ouzounov [45-51]. The comparison between ASDM and CT-SDM is shown in Table 2-4. Both of them have inherent anti-aliasing filters. However, the ASDM has some special properties, including simple circuit design and immunity to clock jitter.

Table 0-4: Comparison between ASDM and CT-SDM

|               | ASDM                                 | CT-SDM                            |  |  |  |  |

|---------------|--------------------------------------|-----------------------------------|--|--|--|--|

| Common        | Inherent anti-aliasing filter        |                                   |  |  |  |  |

|               | Low power or high speed applications |                                   |  |  |  |  |

| Advantages    | Simple circuit (first order)         | Noise shaping                     |  |  |  |  |

|               | Immunity to clock jitter             |                                   |  |  |  |  |

| Disadvantages | Complex decoding scheme              | Complex system (high order)       |  |  |  |  |

|               | Lack of noise shaping                | Sensitive to clock jitter         |  |  |  |  |

|               | Limit cycle components               | • Excess loop delay (instability) |  |  |  |  |

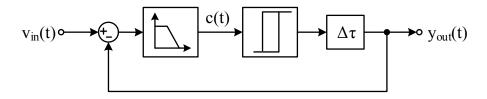

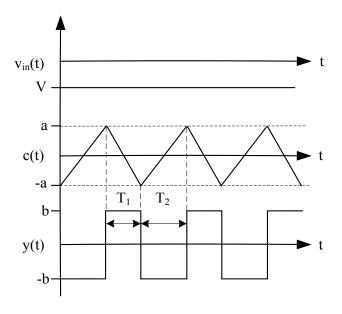

#### 1.7.1System analysis

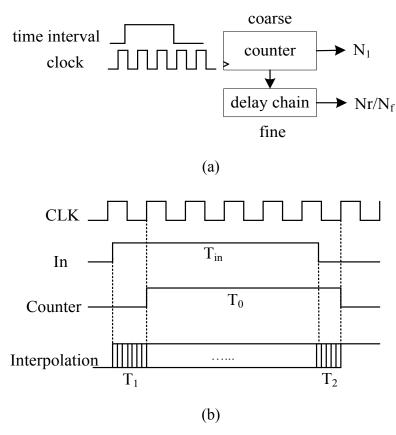

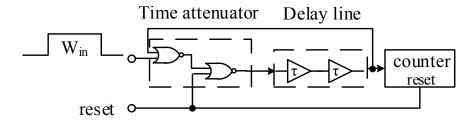

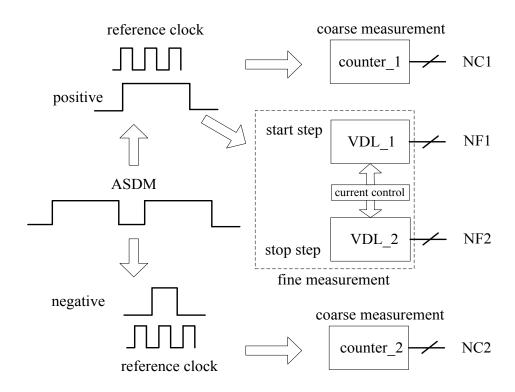

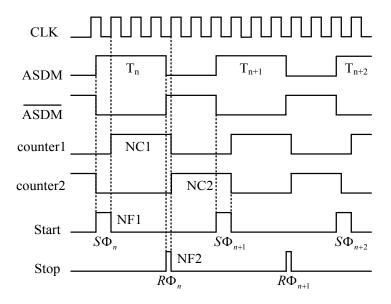

An asynchronous sigma delta modulator (Fig. 2-7(a)) includes two functional blocks: an integrator and a hysteretic comparator. The output (Fig. 2-7(b)) is a pulse width modulated square wave of period T with a pulse-width  $T_1$ . The duty cycle  $\alpha$  is proportional to the amplitude of the input signal (eq. (2-10)). Moreover, the period T of the asynchronous modulator output signal is modulated by the normalized input voltage (eq. (2-11)).

Figure 0-7: (a) System diagram and (b) Timing diagram of the ASDM

(b)

$$\alpha = \frac{V+1}{2} = \frac{T_1}{T_1 + T_2} \tag{2-10}$$

$$\frac{f_0}{f_c} = \frac{T_1}{T_1 + T_2} = 1 - V^2 \tag{2-11}$$

In these expressions  $f_0$  is the output carrier frequency and  $f_c$  is the maximum value of  $f_0$ , namely the limit cycle frequency; |V| < 1 is the normalized input amplitude.

#### 1.7.1.1 Analysis for DC input signal

Waveforms of asynchronous sigma delta modulators for a constant input signal V (|V| < 1) are shown in Fig. 2-8. The output of the modulator is a two level signal of constant duty cycle.

Assuming the integration gain of the loop filter RC = 1, the positive and negative time intervals can be derived as:

$$T_1[n] = \frac{1}{1+V} \cdot \frac{1}{2f_c} \tag{2-12}$$

$$T_2[n] = \frac{1}{1 - V} \cdot \frac{1}{2f_c} \tag{2-13}$$

Where b is the hysteresis of the comparator;  $f_c = 1/4b$  is the limit cycle frequency.

Figure 0-8: Timing diagram of the asynchronous sigma delta modulator with a constant input The square wave with duty cycle  $\alpha$  be represented as:

$$y(t) = 2\alpha - 1 + \frac{4}{\pi} \sum_{n=1}^{\infty} \frac{\sin \alpha n\pi}{n} \cos n\omega_0 t$$

(2-14)

From the block diagram in Fig. 2-8 (a), it can be inferred that:

Where f(t) is the pulse response of the loop filter; c(t) is the output of the loop filter; and  $\otimes$  denotes a convolution.

According to Appendix I, c(t) can be derived as:

$$c(t) = \left[V - (2\alpha - 1)\right]F(0) - \frac{4}{\pi} \sum_{n=1}^{\infty} \frac{\sin \alpha n\pi}{n} \cdot \left[\operatorname{Re}F(n\omega_0)\cos n\omega_0 t - \operatorname{Im}F(n\omega_0)\sin n\omega_0 t\right]$$

(2-16)

Based on the boundary conditions:

$$\begin{cases} y(t_1) = 1, c(t_1) = b, t_1 = -\frac{T_1}{2} + k(T_1 + T_2) \\ y(t_2) = -1, c(t_2) = -b, t_2 = \frac{T_1}{2} + k(T_1 + T_2) \end{cases}$$

(2-17)

Addition and subtraction of eq. (2-16) based on conditions results in:

$$\begin{cases}

\left[V - (2\alpha - 1)\right]F(0) = \frac{4}{\pi} \sum_{n=1}^{\infty} \frac{\sin \alpha n\pi}{n} \operatorname{Re} F(n\omega_0) \cos n\omega_0 \frac{T_1}{2} \\

\sum_{n=1}^{\infty} \frac{\sin^2 n\omega_0 \frac{T_1}{2}}{n} \operatorname{Im} F(n\omega_0) = -\frac{\pi b}{4}

\end{cases}$$

(2-18)

Assuming the loop filter is an ideal integrator with a transfer function of:

$$F(\omega) = -\frac{1}{j\omega} \tag{2-19}$$

After a little algebraic manipulation we get the expressions for the frequency and duty cycle of the output signal:

$$\begin{cases}

\alpha = \frac{1+V}{2} \\

f_0 = f_c \cdot (1-V^2)

\end{cases}$$

(2-20)

When a zero input is applied, the output of the asynchronous sigma delta modulator is a square wave with duty cycle of 50%. The frequency of the output then reaches its maximum value named as the limit cycle frequency.

#### 1.7.1.2 Analysis for a sinusoidal input signal

With a non-trivial input the system becomes complex to analyse. However, if we assume the input signal is slow changing, in other words, the output instantaneous frequency of the modulator is much higher than that the input signal,  $f_c/f_{in} >> 1$ , the expression of eq. (2-16) is still valid in one period,  $T_m \le t \le T_{m+1}$ .

We assume that the input is  $v_{in} = V \cos \mu t$ , with |V| < 1, normalized to the power supply. Here we rewrite the input signal as  $v_{in} \left( T_m \right) = \sum_{m=1}^{\infty} V \cos \mu T_m$ . In one period  $T_m \le t \le T_{m+1}$ , the input signal can be considered to be constant. When  $T_m - T_{m+1} \to 0$ , it becomes the original sine wave. In this case, eq. (2-14) can be rewritten as:

$$y(t) = \sum_{m=1}^{\infty} V \cos \mu T_m + \frac{4}{\pi} \sum_{m=1}^{\infty} \sum_{n=1}^{\infty} \frac{\sin n\pi \left(\frac{1 + V \cos \mu T_m}{2}\right)}{n} \cos n\omega_c \int \left(1 - \frac{V^2 + V^2 \cos 2\mu T_m}{2}\right) dt \quad (2-21)$$

By inserting the boundary conditions eq. (2-15), and based on eq. (I-11) in Appendix I the following equations can be derived:

$$\begin{cases}

\left[V\cos\mu T_{m} - (2\alpha - 1)\right]\operatorname{Re}F\left(\mu\right) = \frac{2}{\pi}\sum_{n=1}^{\infty}\frac{\sin 2\alpha n\pi}{n}\operatorname{Re}F\left(n\omega_{0}\right) \\

\sum_{n=1}^{\infty}\frac{\sin^{2}\alpha n\pi}{n}\operatorname{Im}F\left(n\omega_{0}\right) = -\frac{\pi b}{4}

\end{cases}$$

(2-22)

We are particularly interested in the first harmonic band (n=1) of y(t):

$$y_{1}(t) = \sum_{m=1}^{\infty} \frac{4}{\pi} \cos \frac{\pi V \cos \mu T_{m}}{2} \cos \left[ \omega_{c} \left( 1 - \frac{V^{2}}{2} \right) t - \frac{\omega_{c} V^{2}}{4\mu_{s}} \sin 2\mu T_{m} \right]$$

(2-23)

Here we implement the Jacobi-Anger expansion (Appendix I) to rewrite eq. (2-23) as:

$$y_{1}(t) = \operatorname{Re} \frac{4}{\pi} \sum_{n=-\infty}^{\infty} \sum_{m=-\infty}^{\infty} J_{n}\left(\frac{\pi}{2}V\right) J_{2m}\left(\frac{\omega_{0}V^{2}}{4\mu}\right) e^{in(\pi/2-\mu t)} e^{i2m\mu t} e^{im(\pi/2-\omega t)}$$

(2-24)

It is clear from eq. (2-24), that the amplitudes and frequencies of the Bessel components are a function of both the amplitude and frequency of the input signal and the limit cycle frequency as well. The high-frequency components are tones at frequencies  $f_0 \pm k(2f_{in})$ , where k is an integer number. This holds for small-signal amplitudes,  $f_0 \approx f_c$  as shown in Fig.2-9.

On the other hand, when V is close to the full scale, the output frequency will decrease. The high frequency components are shifting to the low frequency region, and the tails at adjacent harmonics of  $f_0$  are mixed, as shown in Fig.2-10 Therefore, in practical design, the limit cycle frequency should be set far away from the baseband to avoid these components shifting into signal baseband, and a high order filter is required to attenuate these out-band components.

Figure 0-9: Limit cycle frequency components with a small input signal (V = 0.3)

Figure 0-10: Limit cycle frequency components with a large input signal (V = 0.8)

# 1.7.2 Noise performance

Since the input signal amplitude is continuously encoded into the time domain without loss of information, asynchronous sigma delta modulators can be considered as an infinite sampling frequency version of the conventional synchronous sigma delta modulators. Moreover, as there is no quantiser in the system, asynchronous sigma delta modulators do not suffer of quantisation errors. Hence, the signal-to-noise ratio (SNR) in theory can be very high even for a first-order system. This result can be extended to a slowly varying input signal ( $f_c/f_{in} >> 1$ ), and the signal will be only corrupted by harmonic distortion. According to eq. (2-22), we represent the relationship as:

$$V\cos\mu t - (2\alpha - 1) = -\frac{2}{\pi} \sum_{n=1}^{\infty} \frac{\sin 2\alpha n\pi}{n} \cdot \frac{\operatorname{Re} F(n\omega_0)}{\operatorname{Re} F(\mu)}$$

(2-23)

The distortion occurs mainly in the right hand section in equation above. Therefore, assuming  $\omega_0 = \omega_c \left(1 - V^2\right) << \mu$ , for an ideal integrator (eq. (2-19)), by inserting  $2\alpha = 1 + V \cos \mu t$ , the right hand section of eq. (2-23) can be rewritten as:

$$\frac{2}{\pi} \sum_{n=1}^{\infty} \frac{\sin 2\alpha n\pi}{n} \cdot \frac{\operatorname{Re} F(n\omega_0)}{\operatorname{Re} F(\mu)} \approx \frac{2}{\pi} \sum_{n=1}^{\infty} (-1)^n \frac{\sin V n\pi}{n} \cdot \frac{\mu^2}{\omega_0^2}$$

(2-24)

After a Taylor expansion of  $\sin x$  (appendix I), eq. (2-24) becomes:

$$2\alpha - 1 \approx V \cos \mu t + \frac{1}{6}V \frac{\mu^2}{{\omega_0}^2} \cos \mu t + \frac{\pi^2}{6}V^3 \frac{\mu^2}{{\omega_0}^2} \left(\frac{3}{4}\cos \mu t + \frac{1}{4}\cos 3\mu t\right)$$

(2-25)

The most significant distortion term, the third order harmonic distortion, is:

$$\Delta_3 = \frac{\pi^2 \mu^2}{24\omega_0^2} V^2 = \frac{\pi^2}{24} \cdot \left(\frac{\mu}{\omega_c}\right)^2 \cdot \frac{V^2}{1 - V^2}$$

(2-26)

While in practice, the pole of the loop filter is non-zero. For first order loop filter:

$$F(\omega) = \frac{a}{j\omega + p_1} \tag{2-27}$$

Eq. 2-26 can be rewritten as:

$$\Delta_3 = \frac{\pi^2}{24} \cdot \frac{\mu^2 + p_1^2}{\omega_0^2 + p_1^2} V^2$$

(2-28)

Figure 0-11: Estimation for SFDR of ASDMs versus filter pole and normalized input voltage  $(B = 3kHz, f_c = 200kHz)$

Fig. 2-11 shows an estimate of SFDR of ASDMs versus signal bandwidth and filter pole. The limit cycle frequency of the modulator is set to 200kHz, and input signal bandwidth is 3kHz. As expected, the pole location of the loop filter will affect SFDR of the modulator. Note that the SFDR of modulators drops approximately 20dB when the pole of the loop filter is equal to the signal bandwidth. In order to minimize this effect, the pole of the loop filter should be set close to the zero.

If we consider a second order loop system:

$$F(\omega) = \frac{a(j\omega + z_1)}{(j\omega + p_1) \cdot (j\omega + p_2)}$$

(2-29)

The third harmonic distortion can be rewritten as:

$$\Delta_{3} = \frac{\pi^{2}}{24} \cdot \frac{\operatorname{Re} F(\omega_{0})}{\operatorname{Re} F(\mu)} V^{2} \approx \frac{\pi^{2}}{24} \cdot \frac{\left(\mu^{2} + p_{1}^{2}\right)\left(\mu^{2} + p_{2}^{2}\right)}{\left(\omega_{0}^{2} + p_{1}^{2}\right)\left(\omega_{0}^{2} + p_{2}^{2}\right)} \cdot \frac{\omega_{0}^{2}}{\mu^{2}} V^{2} \approx \frac{\pi^{2}}{24} \cdot \frac{\mu^{2}}{\omega_{0}^{2}} V^{2}$$

$$\text{Where } \omega_{0} = \frac{p_{1}p_{2}\pi}{2bz_{1}} \cdot \frac{V^{2}}{1 - V^{2}}, \ p_{1}, p_{2} << \mu << \omega_{0}$$

According to eq. (2-29), increasing the order of the loop filter will only slightly improve the SFDR of the modulator. This is quite different from synchronous sigma delta modulators, where a high order loop filter increases drastically the noise shaping performance. The SFDR versus filter pole frequency for second-order loop filter with a double pole ( $p_1 = p_2$ ) is shown in Fig. 2-12. Although the higher order loop filter has a slightly better performance than the first order loop filter for an ideal double integrator (the pole at zero frequency), the high order system is in practice more sensitive to the location of the pole. For the poles at 5kHz, the SFDR of the second order modulator drops to 25dB from 82dB. For the first order modulation, the SFDR reduces to 52dB down from 81dB.

We conclude that performance with first order loop filter is better than with higher order filters, as the first order loop is less sensitive to the filter poles. As long as the limit cycle frequency is sufficiently higher than the signal bandwidth, a first order loop filter suffices for an asynchronous sigma delta modulator to achieve a high SFDR. This will also much simplify the circuit of asynchronous sigma delta modulators than that of synchronous ones. This implies that asynchronous sigma delta modulators have great potential in both low power and high frequency applications.

Figure 0-12: Comparison of SFDR between the first order and second loop filters versus pole location (B = 3kHz, V = 0.8,  $f_c = 200kHz$ )

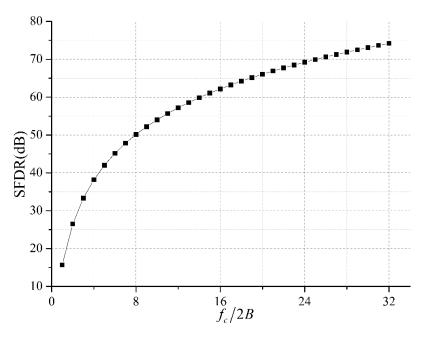

A simulation of the achievable spurious free dynamic range (SFDR) of the first order ASDM with normalized input voltage of 0.8 is shown in Fig.2-13. The pole of the loop filter is set to 1kHz. The horizontal axis is the carrier-to-bandwidth ratio, which is the ratio between the limit cycle frequency and the signal bandwidth. This ratio is in a sense similar with the oversampling ratio in synchronous sigma delta modulators; it determines the minimal limit cycle frequency required for a certain conversion accuracy. For example, in order to obtain a SFDR of 75dB for a signal bandwidth of 1kHz with a first order modulator, the limit cycle frequency has to be at greater than 32kHz.

Figure 0-13: Estimation for the achievable SFDR of the first order ASDM (V = 0.8,  $f_{in} = B/3$ ,  $p_1 = 1kHz$ )

## 1.7.3 Propagation delay

Similar with the conventional synchronous continuous time sigma delta modulators, propagation delay is also an issue in asynchronous sigma delta modulators. In this section, the analysis of the propagation delay is presented.

An asynchronous sigma delta modulator can be modelled as in Fig. 2-14 The propagation delay can be considered as a time shift, which in s-domain is modelled as a multiplicative factor of  $e^{\Delta \tau s}$ . Similar with the system analysis presented earlier, the effect of the propagation delay will be analysed in two conditions: DC and single frequency sinusoidal inputs.

Figure 0-14: System diagram of an asynchronous sigma delta modulator with propagation delay

## 1.7.3.1 DC input signal

The propagation delay in the system results in an overshoot of the output of the loop filter. This increases the effective value of hysteresis. In Fig. 2-15 the timing diagram is shown with a DC input signal applied. And the positive and negative time intervals are:

$$T_{1}[n] = \frac{T_{c}}{2} \cdot \frac{1}{1 - V} + \Delta t_{1}[n] + \Delta t_{2}[n]$$

(2-31)

$$T_{2}[n] = \frac{T_{c}}{2} \cdot \frac{1}{1+V} + \Delta t_{3}[n] + \Delta t_{4}[n]$$

(2-32)

Where  $\Delta t_1[n]$ ,  $\Delta t_2[n]$  and  $\Delta t_3[n]$ ,  $\Delta t_4[n]$  are the overshoot time in the positive and negative time intervals respectively.

Figure 0-15: Time diagram of asynchronous sigma delta modulators with propagation delay

The overshot of the loop filter is:

$$\begin{cases} b_1 = k_n \Delta \tau + b \\ b_2 = k_p \Delta \tau + b \end{cases}$$

(2-33)

Where  $k_p = 1 - V$ ,  $k_p = 1 + V$

Hence the relationship between delay times in each time interval can be shown to be:

$$\Delta t_3[n] = \frac{k_p[n]}{k_n[n]} \Delta t_2[n] = \frac{1 - V}{1 + V} \Delta t_2[n]$$

(2-34)

$$\Delta t_4[n] = \frac{k_p[n]}{k_p[n+1]} \Delta t_1[n+1] = \frac{1-V}{1+V} \Delta t_1[n]$$

(2-35)

Where  $\Delta t_1 [n] = \Delta t_1 [n+1] = \Delta t_1$ .

In this case the output instantaneous frequency of the modulator becomes:

$$T_0 = \frac{T_c}{2} \cdot \frac{2}{(1+V)\cdot(1-V)} + \Delta t_2[n] \frac{2}{1+V} + \Delta t_1[n] \frac{2}{1+V}$$

(2-36)

When the input is zero, the limit cycle frequency becomes:

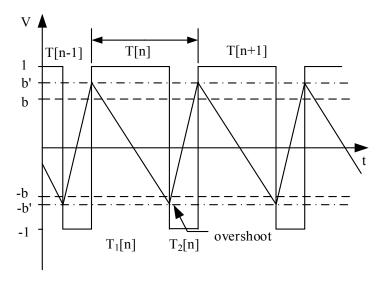

$$f_c' = \frac{1}{4(b+\Delta\tau)} \tag{2-37}$$

Where  $b + \Delta \tau$  is the effective value of the hysteresis.

Note that the propagation loop delay results in a decrease of the limit cycle frequency. Fig. 2-16 the variation of the limit cycle frequency versus the propagation loop delay is shown. When the ratio of  $\Delta \tau/T_c$  increases to 0.1, the limit cycle frequency reduces to  $0.72 f_c$ . This issue will become critical in communication applications, such as bluetooth, WIFI, WiMax and CDMA. This is because the maximum limit cycle frequency is bound by the propagation loop delay, which is equal to  $1/4\Delta\tau$ . This imposes a limitation on the signal bandwidth. The maximum limit cycle frequency reported now right is 250MHz with a signal bandwidth of 8MHz.

Figure 0-16: Variation of the limit cycle frequency versus the propagation loop delay

According to Fig. 2-15, the duty cycle of the output waveform can be easily derived as:

$$\alpha = \frac{T_1[n]}{T_c} = \frac{\frac{T_c}{2} \cdot \frac{1}{1 - V} + \Delta t_1[n] + \Delta t_2[n]}{\frac{T_c}{2} \cdot \frac{2}{(1 + V) \cdot (1 - V)} + \Delta t_2[n] \frac{2}{1 + V} + \Delta t_1[n] \frac{2}{1 + V}} = \frac{1 + V}{2}$$

(2-38)

Here we assume that the propagation delay in the loop is constant. Note that for a DC input signal V, the propagation delay will not affect the duty cycle of asynchronous sigma delta modulators.

# 1.7.3.2 The sinusoidal input signal

For a sinusoidal input signal eq. (2-13) can be rewritten as:

$$\left[ v_{in} - y(t - \Delta \tau) \right] \otimes f(t) = c(t)$$

(2-39)

Using the convolution theorem (Appendix II), the following equations can be obtained:

$$\left[V\cos\mu T_{m} - (2\alpha - 1)\right]\operatorname{Re}F\left(\mu\right) = \frac{2\sqrt{2}}{\pi}\sum_{n=1}^{\infty}(-1)^{n}\frac{\sin2\alpha n\pi}{n}\operatorname{Re}F\left(n\omega_{0}\right)\sin\left(2\pi\frac{\Delta\tau}{T_{0}} + \frac{\pi}{4}\right) + a\frac{\Delta\tau}{T_{c}}V\cos\mu T_{m} \qquad (2-40)$$

$$\sum_{n=1}^{\infty}\frac{\sin^{2}\alpha n\pi}{n}\operatorname{Im}F\left(n\omega_{0}\right)\sin\left(2\pi\frac{\Delta\tau}{T_{0}} + \frac{\pi}{4}\right) = -\frac{\pi\left(b + a\frac{\Delta\tau}{T_{c}}\right)}{4\sqrt{2}}$$

Where

$$a = \frac{4}{A_0 \cdot b}$$

.

Note that the propagation loop delay introduces a bias drift to the modulator, which has the same shape and phase of the input signal as shown in Fig. 2-17.

Figure 0-17: Phenomenon of propagation delay

For an ideal integrator, the third order harmonic distortion can be derived as:

$$\Delta_3 = \frac{\sqrt{2}\pi\mu^2}{24\omega_0^2}\sin\left(2\pi\frac{\Delta\tau}{T_0} + \frac{\pi}{4}\right) \tag{2-41}$$

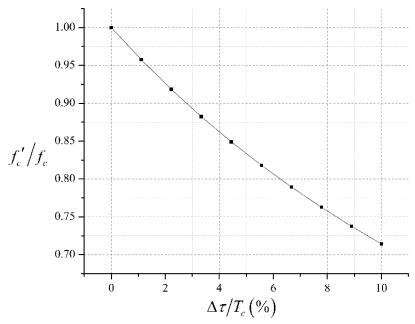

Compared with eq. (2-27), the propagation loop delay results in the distortion function a factor  $\sqrt{2}\sin\left(2\pi\frac{\Delta\tau}{T_0} + \frac{\pi}{4}\right)$ . The SFDR versus the propagation loop delay is shown in Fig. 2-18. Note

that  $0.1T_c$  will result in a 8.5dB decrease in SFDR. It can therefore be concluded that the propagation loop delay limits the limit cycle frequency of asynchronous sigma delta modulators, which in turn limits the signal bandwidth if the SFDR of the system is maintained to a certain level. For example, for a 40ps loop delay, the limit cycle frequency will be limited to 250MHz in order to maintain the value of  $\Delta \tau / T_c$  within 1%.

Figure 0-18: SFDR of asynchronous sigma delta modulators with propagation loop delay

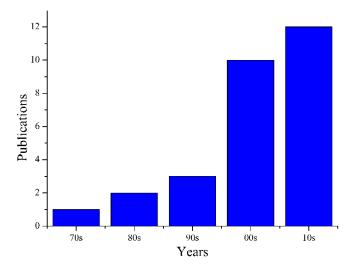

#### 1.7.4 The state-of-art of asynchronous sigma delta modulators

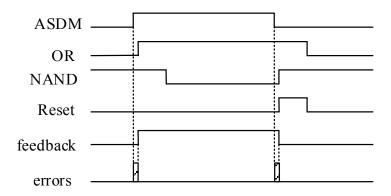

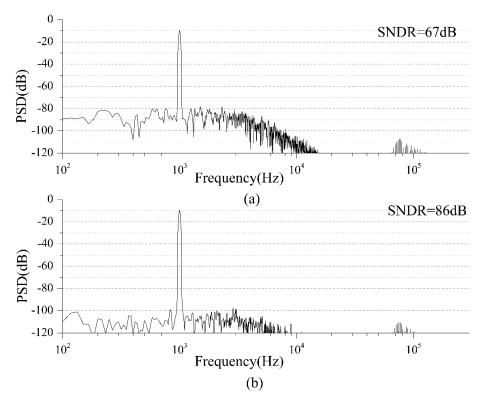

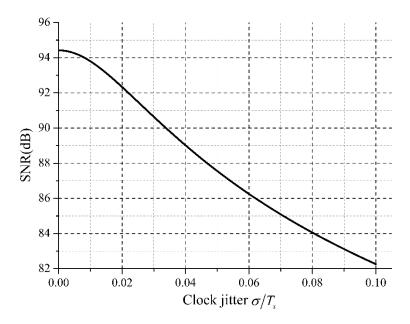

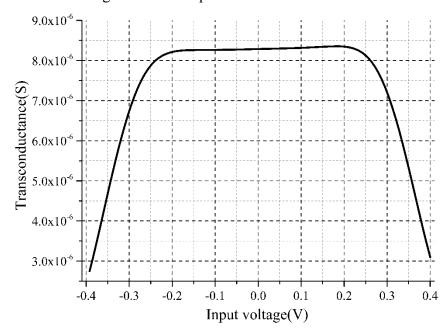

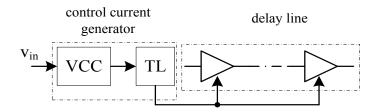

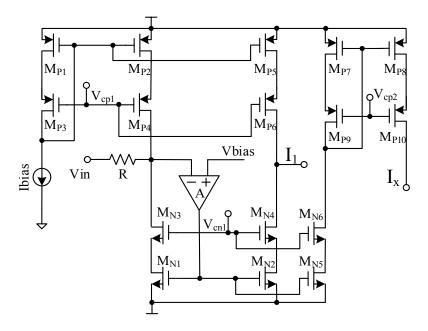

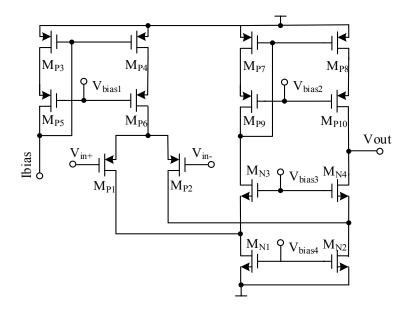

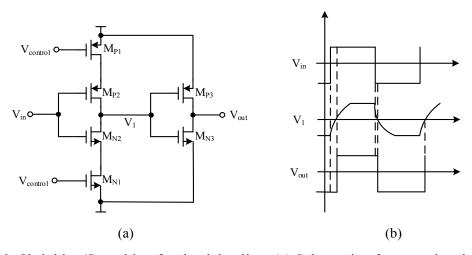

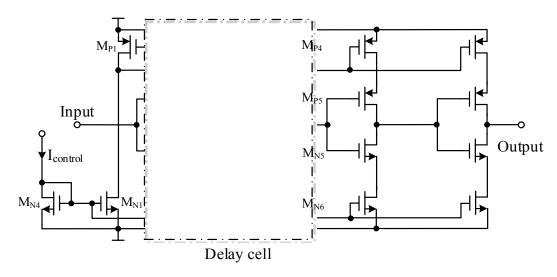

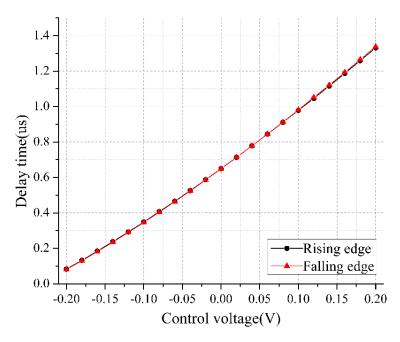

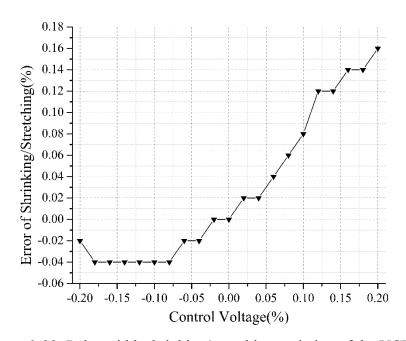

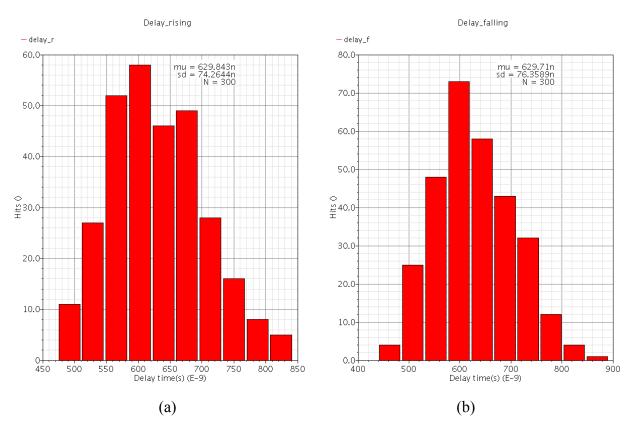

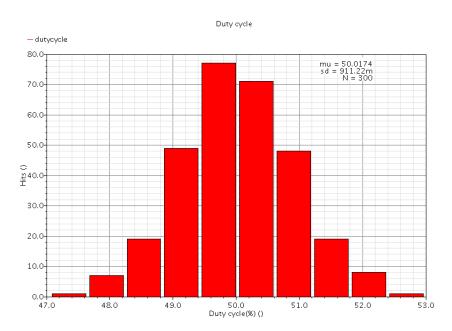

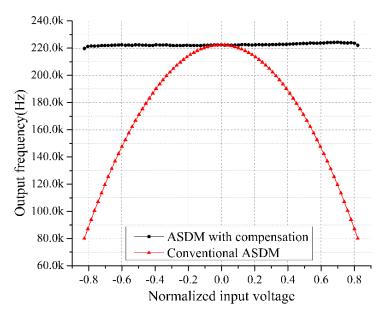

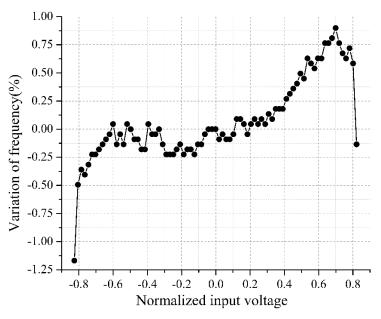

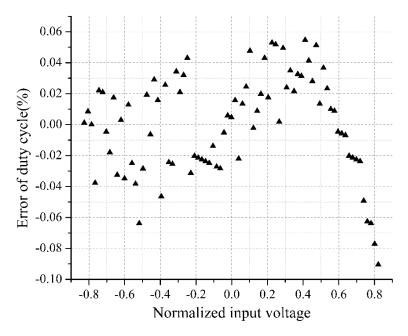

Asynchronous sigma delta modulators were first proposed in 1975. Very few publications have appeared over nearly 35 years (Fig. 2-19). This is because synchronous sigma delta modulators were very robust with the effect of oversampling and noise shaping. However, the conventional signal delta modulator is reaching its limits of acceptable power consumption and the maximum speed supported by CMOS technology. During the last 10 years, asynchronous sigma delta modulators have been increasing explored as a potential solution of the problems associated with